# IPC-7091A

# Design and Assembly Process Implementation of 3D Components

Developed by the 3D Electronic Packages Guideline Task Group (B-11a) of the Packaged Electronic Components Committee (B-10) of IPC

# Supersedes:

IPC-7091 - June, 2017

Users of this publication are encouraged to participate in the development of future revisions.

Contact:

**IPC**

Tel 847 615.7100 Fax 847 615.7105 January 2023 IPC-7091A

# **Table of Contents**

| 1      | <b>SCOPE</b> 1                              | 3.3      | Embedded Circuitry Technology 9                       |

|--------|---------------------------------------------|----------|-------------------------------------------------------|

| 1.1    | Purpose                                     | 3.4      | Advanced Packages                                     |

| 1.1.1  | Target Audience                             | 4 DE     | VICE CONSIDERATIONS                                   |

| 1.1.2  | Intent                                      | 4.1      | Package Assembly Variations                           |

| 1.2    | Classification                              | 4.1.1    | Die Stack (Wire Bond)                                 |

| 1.3    | Measurement Units                           | 4.1.2    | Package-on-Package (PoP) Technologies 11              |

| 1.4    | Use of "Lead"                               | 4.1.3    | Through Mold Via (TMV)                                |

| 1.5    | Abbreviations and Acronyms 1                | 4.1.4    | Through-Mold Interconnect (TMI)                       |

| 1.6    | Terms and Definitions                       | 4.1.5    | High-Density Package-on-Package (PoP)12               |

| 1.6.1  | Die                                         | 4.1.5.1  | Cu Pillar Interconnect (CuPI)                         |

| 1.6.2  | Electronic Element                          | 4.1.5.2  | Micro-Pillar (μPILR)                                  |

| 1.6.3  | Interposer                                  | 4.1.5.3  | Bond Via Array (BVA)                                  |

| 1.6.4  | Substrate                                   | 4.1.5.4  | Direct-Bond Interconnect (DBI)                        |

| 1.6.5  | Electronic Package                          | 4.1.6    | Folded Stack Packaging                                |

| 1.6.6  | Electronic Module 2                         | 4.1.7    | Package-on-Package Interposer (PoPi)                  |

| 1.6.7  | Three-Dimensional (3D) Packaging 2          | 4.1.8    | Thin Small Outline Package (TSOP)                     |

| 1.7    | Implementation Challenges 2                 |          | Stacking                                              |

| 2      | APPLICABLE DOCUMENTS                        | 4.1.9    | High Band Memory (HBM)                                |

| 2.1    | IPC                                         | 4.1.9.1  | Silicon Bridge Interposer                             |

| 2.2    | Joint Industry Standards 4                  | 4.1.9.2  | Embedded Multi-Die Interconnect Bridge                |

| 2.3    | JEDEC 4                                     |          | (EMIB)                                                |

| 2.4    | Government Electronics and Information      | 4.1.10   | Die/Wafer Stack Cu-to-Cu                              |

|        | Technology Association (GEIA)4              | 4.1.10.1 | Cu-Sn-Cu Fusion Bond                                  |

| 3      | GENERAL DESCRIPTION 4                       | 4.1.10.2 | Thermocompression Bonding                             |

| 3.1    | Technology Overview 4                       | 4.1.10.3 | Adhesion Bonding                                      |

| 3.1.1  | Die Stack Package                           | 4.1.11   | Three-Dimensional (3D) Interposer/Substrate Packaging |

| 3.1.2  | Package Stack 5                             | 4.2      | General Requirements                                  |

| 3.1.3  | Package-on-Package (PoP) 5                  | 4.3      | Device Preparation                                    |

| 3.1.4  | Interposer                                  | 4.3.1    | Cleaning                                              |

| 3.1.5  | Through-Silicon Via (TSV)6                  | 4.3.2    | Baking                                                |

| 3.1.6  | Through-Glass Via (TGV) 6                   | 4.3.3    | Changing Termination Material                         |

| 3.1.7  | System on Chip (SoC)                        | 4.3.3.1  | Deballing                                             |

| 3.1.8  | System in Package (SiP) 6                   | 4.3.3.2  | Reballing                                             |

| 3.1.9  | Wafer-Level Packaging (WLP)6                | 4.3.3.3  | Outsourcing Solutions                                 |

| 3.1.10 |                                             | 4.3.3.4  | Mixed/Backward Compatibility                          |

| 3.1.11 |                                             | 1.5.5.1  | Solder Processing                                     |

| 3.2    | Package Geometric Space                     | 4.3.3.5  | Underfill for Mixed-Alloy Soldering 20                |

| 3.2.1  | Two-Dimensional (2D) Package                | 4.4      | Passive-Component Integration                         |

| 3.2.2  | Two-and-a-Half-Dimensional (2.5D) Package 8 |          | (Organic Base Material)                               |

| 3.2.3  | Three-Dimensional (3D) Package 8            | 4.4.1    | Formed Resistors                                      |

|        | , , , , , , , , , , , , , , , , , , ,       | 4.4.1.1  | Etch-Formed Resistors                                 |

IPC-7091A January 2023

| 4.4.1.2<br>4.4.2 | Discrete Resistors                                | 5.8     | Conductor Characteristics (Metallization on Ceramic) |

|------------------|---------------------------------------------------|---------|------------------------------------------------------|

| 4.4.2.1          | Discrete (Placed) Capacitors                      | 6 PR    | OCESS MATERIALS33                                    |

| 4.4.3            | Formed Inductors                                  | 6.1     | Adhesives (Conductive and Nonconductive) 33          |

| 4.4.4            | Discrete Inductors                                | 6.1.1   | Polymer Adhesives                                    |

| 4.5              | Passive Component Integration                     | 6.1.1.1 | Thermoset Materials                                  |

| 4.5              | (Nonorganic Base Material)                        | 6.1.1.2 | Thermoplastic Materials                              |

| 4.5.1            | Formed Resistors                                  | 6.1.2   | Dry-Film Adhesive                                    |

| 4.5.2            | Formed Capacitors                                 | 6.1.2.1 | Die-Attach Film Application                          |

| 4.5.3            | Formed Inductors                                  | 6.2     | Solder Materials                                     |

| 4.6              | Semiconductor Die Issues                          |         |                                                      |

| 4.6.1            | Surface Redistribution                            |         | CKAGE-LEVEL STANDARDIZATION                          |

| 4.7              | Postprocess Validations                           | 7.1     | Package Outline Standards                            |

| 4.7.1            | Solder on Pad (Flip-Chip)                         | 7.1.1   | Ball Grid Array (BGA)                                |

| 4.7.2            | Known Good Die (KGD)                              | 7.1.2   | Fine-Pitch BGA (FBGA/FIBGA)                          |

| 4.8              | Component Handling                                | 7.1.3   | Package-on-Package (PoP)                             |

| 4.8.1            | Packaging                                         | 7.1.4   | Through-Mold Via (TMV) Package-on-Package (PoP)      |

| 4.8.2            | Component Storage                                 | 7.1.5   | Wafer-Level Ball Grid Array (WLBGA) 38               |

| 4.9              | Thermal Management of 3D Components 25            | 7.1.6   | Stacked-Die Packaging Standards                      |

| 4.9.1            | Thermal Conduction/Convection                     | 8 PRI   | NTED BOARD AND OTHER MOUNTING                        |

| 4.9.2            | Thermal Transfer Mechanisms                       |         | SE OR BOARD STACK-UP                                 |

| 4.9.3            | Advanced Thermal Interface Materials 26           | СО      | NSIDERATIONS                                         |

| 4.9.4            | High-Conductivity Mold Compounds28                | 8.1     | Printed Board Technology                             |

| 4.9.5            | Liquid Cooling                                    | 8.1.1   | Multilevel Substrate                                 |

| 4.9.6            | Microfluidic Cooling                              | 8.2     | Mounting Base                                        |

| 4.9.7            | Single-Phase Intertier Cooling                    | 8.3     | Surface Finish for Placed Components 40              |

| 4.9.8            | Two-Phase Intertier Cooling                       | 8.3.1   | Electroless Nickel/Immersion Gold (ENIG) 40 $$       |

| 4.9.9            | Heat Pipes                                        | 8.3.2   | Electroless Nickel/Electroless                       |

| 4.9.10           | Microchannel and Minichannel Cooling29            |         | Palladium/Immersion Gold (ENEPIG) 40                 |

| 4.9.11           | Thermal Modeling                                  | 8.3.3   | Organic Solderability Preservative (OSP)40           |

| 4.10             | Cost Consideration                                | 8.3.4   | Electrolytic Nickel/Electrolytic Gold (ENEG)         |

| 5 INT            | ERPOSER/SUBSTRATE MATERIALS 30                    | 8.3.5   | Direct Immersion Gold (DIG)                          |

| 5.1              | Organic Interposer                                | 8.3.6   | Immersion Silver                                     |

| 5.1.1            | Organic, CTE Matching Interposer Material31       | 8.3.7   | Immersion Tin                                        |

| 5.1.2            | Organic-Based Interposer Fabrication Process . 31 | 8.3.8   | Cu (Chemical Deposition and Electroplate) 41         |

| 5.2              | Glass Interposer                                  | 8.4     | Embedded-Component Technology                        |

| 5.3              | Silicon Interposers                               | 8.4.1   | Formed Resistor Process                              |

| 5.4              | Ceramic Substrate/Interposer                      | 8.4.1.1 | Design Criteria for Sheet-Film-Type Resistor         |

| 5.5              | Conductor Characteristics (Cu Foil/Film)32        | 0.4.1.1 | Elements                                             |

| 5.6              | Conductor Characteristics (Cu Toll/Tillil)32      | 8.4.2   | Capacitor Formation Process                          |

| 5.0              | (Metallization on Silicon)                        | 8.4.3   | Planar Capacitance                                   |

| 5.7              | Conductor Characteristics                         | 8.4.3.1 | Plane Layer Separation                               |

|                  | (Metallization on Glass)                          | 8.4.4   | Discrete Formed Capacitor Element 42                 |

|                  |                                                   |         | •                                                    |

| 8.4.5     | Discrete Inductor Forming 42                                    | 9.2.1.2      | Ceramic-Based Interposer Design                           | 50         |

|-----------|-----------------------------------------------------------------|--------------|-----------------------------------------------------------|------------|

| 8.4.6     | Discrete Component Placement 43                                 | 9.2.2        | External (Surface) Component Mounting 5                   | 50         |

| 8.4.6.1   | Discrete Resistor and Capacitor Placement 43                    | 9.2.2.1      | Solder Attachment                                         | 50         |

| 8.4.6.2   | Discrete Inductor Placement                                     | 9.2.2.2      | Conductive Polymer Attachment                             | 50         |

| 8.4.6.3   | Active-Die Element Placement                                    | 9.2.3        | Internal (Embedded) Component Mounting 5                  | 50         |

| 8.4.6.4   | Surface Finishes for UBM Plating 44                             | 9.2.4        | Circuit Interface Techniques                              | 50         |

| 8.4.6.4.1 | Electroless Nickel/Immersion Gold (ENIG) 44                     | 9.2.4.1      | Organic-Based Interposer Design                           | 50         |

| 8.4.6.4.2 | Electroless Nickel/Electroless                                  | 9.2.5        | Internal Discrete Heat Sink                               | 52         |

|           | Palladium/Immersion Gold (ENEPIG) 44                            | 9.2.5.1      | Organic-Based Interposer Design                           | 52         |

| 8.4.6.4.3 | Cu Under-Bump Metallization                                     | 9.3          | Layout Strategy                                           | 52         |

| 8.4.6.5   | (UBM) Plating                                                   | 9.3.1        | Product Functional Description                            | 52         |

| 8.4.6.3   |                                                                 | 9.3.2        | Engineering Actions                                       | 52         |

| 8.3       | Substrate and Interposer Materials (Package Level)              | 9.3.3        | Design Density Analysis                                   | 52         |

| 8.5.1     | Organic Circuit Structure                                       | 9.3.4        | Embedded Component Selection                              | 53         |

| 8.5.2     | Ceramic Circuit Structure                                       | 9.3.4.1      | Embedding Passive Components                              | 53         |

| 8.5.2.1   | Metallization on Ceramic                                        | 9.3.4.2      | Embedding Active Components                               | 53         |

| 8.5.3     | Silicon Circuit Structure                                       | 9.3.5        | Embedded-Component Circuit Interface 5                    | 53         |

| 8.5.4     | Glass Circuit Structure                                         | 9.4          | Multilayer Substrate Construction                         |            |

| 8.6       | Dielectric Impregnation                                         |              | and Geometries                                            | 54         |

| 8.6.1     | Reinforced Prepreg                                              | 9.4.1        | Build-Up Circuit Layers on Glass Base Structures          | 54         |

| 8.6.2     | Unreinforced Resin                                              | 9.4.2        | Build-Up Circuit Layers on                                |            |

| 8.6.3     | Resin-Coated Cu (RCC)                                           |              | Silicon Base Structures                                   | 54         |

| 8.7       | Via Hole Preparation and Interconnectivity 46                   | 9.5          | Component Attachment on                                   |            |

| 8.7.1     | Through-Glass Via (TGV) Connection to                           |              | Multilevel Assembly                                       |            |

|           | Printed Board Cu                                                | 9.5.1        | Conductive Polymers                                       |            |

| 8.7.2     | Through-Glass Via (TGV) Connection to Component Terminations 46 | 9.5.2        | Dry-Film Adhesives                                        |            |

| 8.7.3     | Through-Glass Via (TGV) Formation 46                            | 9.5.3        | Solder Attachment                                         | 55         |

| 8.7.4     | Through-Silicon Via (TSV) Formation 47                          | 9.6          | Circuit Routing Strategy (Organic and Nonorganic)         | <i>5 5</i> |

| 8.7.5     | Via Filling                                                     | 9.6.1        | Organic-Based Substrates                                  |            |

| 8.7.6     | Alternative Via Plating on                                      | 9.6.2        | Silicon and Glass Interposers                             |            |

| 8.7.0     | Silicon-Based Interposers                                       | 9.6.2        | Ī                                                         |            |

| 8.7.7     | Conductor Forming on Silicon Interposers 48                     | 9.0.3<br>9.7 | Ceramic-Based Substrates and Interposers 5  Documentation |            |

| 8.8       | Build-Up Layers and Via Hole Preparation –                      | 9.7.1        | Documentation Package                                     |            |

|           | Redistribution Layer (RDL) on                                   | 9.7.1        | Bill of Materials (BoM).                                  |            |

|           | Silicon and Glass                                               |              |                                                           |            |

| 8.8.1     | Silicon Interposer Metallization 48                             | 9.7.3        | Software Tools and Data Transfer                          |            |

| 8.8.2     | Glass Interposer Metallization 48                               | 9.7.4        | General Rules for 3D Design                               | 90         |

| 8.9       | Multilevel Printed Board – Cavity Board 48                      |              | SEMBLY OF 3D PACKAGES ON INTED BOARDS5                    | 56         |

| 9 DE      | SIGN METHODOLOGY49                                              | 10.1         | Package-on-Package (PoP) Assembly Process . 5             |            |

| 9.1       | Design Challenges                                               | 10.1.1       | Package-on-Package (PoP) Fluxing Options 5                |            |

| 9.2       | Total Circuit Consideration 49                                  | 10.1.1       | Package-on-Package (PoP) Fluxing Process5                 |            |

| 9.2.1     | Internal (Embedded) Component Mounting 49                       | 10.1.2.1     | Flux Coverage                                             |            |

| 9.2.1.1   | Organic-Based Interposers 49                                    | 10.1.2.1     | Trun Coverage                                             | ,0         |

| 10.1.2.2 | Dwell Time (Hold Time) Speed 58                    | 10.9.3   | Removable and Reworkable Underfill                                   | 71 |

|----------|----------------------------------------------------|----------|----------------------------------------------------------------------|----|

| 10.1.2.3 | Retracting Speed                                   | 10.9.4   | Corner Bonding/Glue Bonding                                          | 71 |

| 10.1.2.4 | Retracting Force                                   | 10.9.5   | Molded Underfill (MUF)                                               | 71 |

| 10.1.3   | Flux Height Statistical Process Control 58         | 10.9.6   | Vacuum Underfill (VUF)                                               | 72 |

| 10.1.4   | Paste Dip                                          | 10.9.7   | Wafer-Applied Underfill                                              | 72 |

| 10.1.5   | Prestacking Process                                | 10.9.8   | Underfill Inspection                                                 | 72 |

| 10.1.6   | Through-Mold Via (TMV)                             | 10.9.8.1 | Causes of Voids                                                      | 72 |

|          | Assembly Considerations                            | 10.9.8.2 | Void Characteristics                                                 | 73 |

| 10.1.7   | Package-on-Package (PoP) Stand-Off Height (SOH)    | 10.9.8.3 | Test Strategies                                                      | 73 |

| 10.1.8   | Package-on-Package (PoP) Die Gap 60                | 10.9.8.4 | Flow-Pattern Voids                                                   | 73 |

| 10.1.6   | Three-Dimensional (3D) Printing 61                 | 10.9.8.5 | Moisture Voids                                                       | 73 |

| 10.2.1   | Cavity Printing                                    | 10.9.8.6 | Effect of Contamination                                              | 73 |

| 10.2.1   | Jet Printing                                       | 11 TES   | STING AND PRODUCT VERIFICATION                                       | 73 |

| 10.2.3   | Paste Dispensing 61                                | 11.1     | Establishing Test Requirements                                       | 73 |

| 10.2.4   | Cavity Keep-Out Zone                               | 11.2     | Assembly Process Qualification                                       | 74 |

| 10.3     | Multilevel Placement                               | 11.2.1   | Package-Level Stress Test                                            | 74 |

| 10.3.1   | Parameters                                         | 11.3     | Substrate Test Coupons                                               | 75 |

| 10.3.2   | Cavity Design                                      | 12 RE    | LIABILITY                                                            | 75 |

| 10.3.3   | Plateau Design                                     | 12.1     | Reliability Considerations                                           |    |

| 10.4     | Die Attachment                                     | 12.2     | Design for Reliability (DfR) Principles                              |    |

| 10.4.1   | Direct Chip Attachment                             | 12.3     | End-Use Relationship                                                 |    |

| 10.4.2   | Die-to-Substrate Reinforcement 64                  | 12.3.1   | Temperature Cycle Condition                                          |    |

| 10.5     | Reflow Soldering Considerations for                | 12.3.2   | Test Duration                                                        |    |

|          | 3D Components                                      | 12.3.3   | Number of Samples                                                    |    |

| 10.5.1   | Low-Temperature Soldering (LTS) of 3D Components   | 12.4     | Effects of Pb-Free Materials and Pure-Sn Finishes on Reliability     | 78 |

| 10.5.1.1 | Drivers for Low-Temperature Solders in 3D Assembly | 12.5     | Validation, Qualification and Accelerated Aging Test for Reliability |    |

| 10.5.1.2 | Choice of Low-Temperature Solder Alloys 66         | 12.6     | Environmental Testing                                                |    |

| 10.5.1.3 | Mixed-Alloy LTS-SAC (Hybrid Joint)67               | 13 DE    | FECT AND FAILURE ANALYSIS                                            |    |

| 10.6     | 3D Component Inspection Techniques 67              | 13.1     | Nondestructive Failure Analysis                                      |    |

| 10.6.1   | X-Ray Inspection Techniques 67                     | 13.1.1   | Electrical Testing.                                                  |    |

| 10.6.2   | Acoustic Microscopy (AM)                           | 13.1.1   | Functional Testing (FT).                                             |    |

| 10.7     | Inspection Techniques                              | 13.1.1.2 | Modeled Fault Testing (MFT)                                          |    |

| 10.7.1   | Rework with Convection Reflow Soldering 70         | 13.1.1.3 | Iddq                                                                 |    |

| 10.7.1   | Rework with Infrared (IR) Reflow Soldering 70      | 13.1.1.4 | Time-Domain Reflectometer (TDR)                                      |    |

| 10.7.2   | Rework with Laser Soldering                        | 13.2     | Internal Nondestructive Inspection                                   |    |

| 10.7.3   | Underfill                                          | 13.2.1   | Acoustic Microscopy (AM).                                            |    |

| 10.8.1   | Package-to-Printed Board Reinforcement71           | 13.2.2   | X-Ray Imaging                                                        |    |

| 10.9     | Material Selection and Application                 | 13.2.3   | Infrared (IR).                                                       |    |

| 10.9.1   | Capillary Flow Underfill                           | 13.2.3.1 | Infrared (IR) Thermography (IRT)/Thermal                             | -  |

| 10.9.2   | No-Flow/Fluxing Underfill                          |          | Imaging                                                              | 80 |

|          |                                                    |          |                                                                      |    |

| 13.2.3.2         | Infrared (IR) Microscopy                                                         | Figure 3-8  | Example of a 2.5D System in Package (SiP)8                                    |

|------------------|----------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------|

| 13.2.4<br>13.2.5 | Magnetic Current Imaging (MCI)                                                   | Figure 3-9  | 3D Package-on-Package (PoP) and System                                        |

| 13.2.5           | Internal Optical Inspection                                                      | C           | in Package (SiP) on a Printed Board 8                                         |

| 13.2.7           | Chemical Analysis                                                                | Figure 3-10 | Ball Grid Array (BGA) Substrate with Embedded Active and Passive Elements 9   |

| 13.3             | Destructive Failure Analysis 81                                                  | Figure 3-11 | Advanced Package Trends 9                                                     |

| 13.3.1           | Cross-Sectioning                                                                 | Figure 4-1  | Comparing Current Two-Die and                                                 |

| 13.3.2           | Parallel Lapping                                                                 |             | Quad-Die Package Solutions                                                    |

| 13.3.3           | Decapsulation                                                                    | Figure 4-2  | Standard Package-on-Package (PoP)                                             |

| 13.4             | Optical Inspection                                                               | E: 4.2      | Example with Stacked Die                                                      |

| 13.4.1           | Optical Inspection (After Assembly) 82                                           | Figure 4-3  | Through-Mold Via (TMV) Package-on-Package (PoP)11                             |

| 13.4.2           | Confocal Laser Scanning Microscopy (CLSM)                                        | Figure 4-4  | Lower Package-on-Package (PoP) Section with Through-Mold Vias (TMVs)          |

| 13.5             | Examples of Observed External Inspection                                         | Figure 4-5  | Through-Mold Via (TMV) Solder Balls11                                         |

| 13.5.1           | Defects                                                                          | Figure 4-6  | Lower Package-on-Package (PoP) Section with Through Mold Interconnect (TMI)12 |

| 13.5.2           | Package-on-Package (PoP) Joining Defects 83                                      | Figure 4-7  | Cu Pillar Interconnect (CuPI)                                                 |

| 13.5.3           | Nonwet Open (NWO) Joint                                                          | T: 4.0      | Package-on-Package (PoP)                                                      |

| 13.5.4<br>13.5.5 | Bridging on Package-on-Package (PoP) 83 Through-Mold Via Head on Pillow (HoP) 83 | Figure 4-8  | High-Density Micro-Pillar (μPILR) Array Packaging                             |

| 13.5.6           | Insufficient Solder/Flux84                                                       | Figure 4-9  | Bond Via Array (BVA) With Fine-Pitch Cu Wire Interconnect                     |

| 13.5.7           | Incomplete Solder Reflow                                                         | Figure 4-10 | Direct Bond Interface (DBI)14                                                 |

| 13.5.8           | Missing Solder Ball                                                              | Figure 4-11 | Three-Memory Die on Flexible Circuit                                          |

| 13.5.9           | Nonuniform or Missing Solder Deposition 84                                       |             | Substrate                                                                     |

| 13.5.10          | Voids and Uneven Solder                                                          | Figure 4-12 | Package-on-Package Interposer (PoPi) 14                                       |

|                  | BASSEMBLY CONTRACTOR SELECTION D QUALIFICATION                                   | Figure 4-13 | Stacked Thin Small Outline Package (TSOP) Devices                             |

| 14.1             | Factory and Process Audits                                                       | Figure 4-14 | High-Band Memory (HBM)15                                                      |

| 14.2<br>14.3     | Site Visit Procedure                                                             | Figure 4-15 | Silicon Bridge Interposer with Stacked Die and HBM                            |

| 14.4             | Observations and Recommendations 86                                              | Figure 4-16 | Embedded Multi-Die Interconnect Bridge                                        |

| Appendix         |                                                                                  |             | (EMIB)                                                                        |

|                  | Figures                                                                          | Figure 4-17 | Through-Silicon Via (TSV)16                                                   |

| Figure 1-        | -                                                                                | Figure 4-18 | Fusion Bond Process                                                           |

| Figure 3-        |                                                                                  | Figure 4-19 | Intermetallic Bonds (Cu/Cu3Sn/Cu) 17                                          |

| Figure 3-        | c ,                                                                              | Figure 4-20 | Intermetallic Thermo-compression Bonding                                      |

| Figure 3-        | •                                                                                | Figure 4-21 | Benchtop Small-Batch Ultrasonic Cleaner                                       |

| Figure 3-        | 4 System in Package (SiP) Example 6                                              | Figure 4-22 | JEDEC-Compliant Carrier Tray                                                  |

| Figure 3-        | Wafer-Level Packaging (WLP) for High-Performance Memory                          | Figure 4-23 | SnPb and Mixed-Metallurgy Ball Grid<br>Array (BGA) Solder Joints              |

| Figure 3-        | 6 Fanout Wafer Level Package Examples 7                                          | Figure 4-24 | Formed Resistor Elements                                                      |

| Figure 3-        | 7 Example of a 2D System in Package 7                                            | Figure 4-25 | Trench or Pillar Capacitor in Silicon 22                                      |

IPC-7091A January 2023

| Figure 4-26 | Surface Redistribution                                                                                      | Figure 8-3   | Pull-Up and Pull-Down Resistors Using Thin-Film Material             |

|-------------|-------------------------------------------------------------------------------------------------------------|--------------|----------------------------------------------------------------------|

| Figure 4-27 | Contact Variations for Flip-Chip Mounting                                                                   | Figure 8-4   | Formed Multilayer Capacitor Element 42                               |

| Figure 4-28 | Partitioned Carrier Trays for Ball Grid                                                                     | Figure 8-5   | Etched Cu Spiral Inductor Pattern                                    |

| Figure 4-29 | Array (BGA) Components                                                                                      | Figure 8-6   | 0603 Components Embedded into a Cavity Feature in the Substrate43    |

| Figure 4-30 | Thermal Conduction                                                                                          | Figure 8-7   | Three-Dimensional (3D) Die Stack Package                             |

| Figure 4-31 | Thermal Transfer Paths                                                                                      | 1 iguic 6-7  | Using Cu Wire-Bond Processing                                        |

| Figure 4-32 | Thermal Resistance Versus Bondline Thickness for State-of-the-Art Thermal                                   | Figure 8-8   | Additive Redistribution Layer (RDL) to Array Contact Site            |

|             | Greases and Gels                                                                                            | Figure 8-9   | Merging Organic and Silicon-Based                                    |

| Figure 4-33 | Advances in Thermal Resistance with                                                                         |              | Materials for 3D Semiconductor Packaging                             |

|             | Thinner and Higher-Conductivity Reliable Materials                                                          | Figure 8-10  | Ceramic-Based Interposer                                             |

| Figure 4-34 | Nanosilver Interconnections                                                                                 | Figure 8-11  | Through-Glass Via (TGV)                                              |

| •           |                                                                                                             | •            |                                                                      |

| Figure 4-35 | Advances in 3D Packages with Fan-Out<br>Wafer-Level Packaging (FOWLP) and                                   | Figure 8-12  | Through-Glass Via (TGV)-Formed Glass Substrates                      |

|             | Die-Embedding (Left) and<br>High-Thermal-Conductivity Composites<br>with Advanced Boron Nitride Fillers and | Figure 8-13  | Metallized Through-Glass Via (TGV) X-Ray Photos                      |

|             | Surface Treatments (Right)28                                                                                | Figure 8-14  | Cu-Filled Through-Silicon Via (TSV)                                  |

| Figure 4-36 | Liquid Heat Pipe Exchange System 28                                                                         |              | Interface Between Wafers – Active Side and Back Side                 |

| Figure 4-37 | Comparison of 3D Integrated Circuits (ICs) Utilizing Different Cooling                                      | Figure 8-15  | Comparing Via Deposition Methodology                                 |

| Figure 5-1  | Technologies                                                                                                | Figure 8-16  | Comparison of Component in a Cavity<br>Versus on the Board Surface48 |

|             | Through-Silicon Via (TSV)                                                                                   | Figure 8-17  | Cavity Design Example                                                |

|             | Interconnects                                                                                               | Figure 9-1   | Embedded Semiconductor Substrate 54                                  |

| Figure 5-2  | Glass Wafer and Panel Substrates                                                                            | Figure 9-2   | Glass Interposer With 40-µm Pitch                                    |

| Figure 5-3  | Microcrystalline-Silicon Ingot                                                                              |              | Bumps and L/S = $2 \mu m / 2 \mu m \dots 54$                         |

| Figure 5-4  | Flattened Feature on Wafer Edge Identifies                                                                  | Figure 9-3   | Two-Layer Build-Up Circuit Interposer 54                             |

|             | Wafer Orientation During Fabrication Processes                                                              | Figure 10-1  | Package-on-Package (PoP) Assembly Principle                          |

| Figure 5-5  | Ceramic Panel Prior to Metallization 32                                                                     | Figure 10-2  | Package-on-Package (PoP)                                             |

| Figure 7-1  | Ball Grid Array (BGA) Package Outline 36                                                                    |              | Fluxing Units57                                                      |

| Figure 7-2  | Fine-Pitch Ball Grid Array                                                                                  | Figure 10-3  | Ball Grid Array (BGA) Flux Coverage58                                |

|             | (FBGA/FIBGA)                                                                                                | _            | Flux Transfer to a Cu Coupon                                         |

| Figure 7-3  | Fine-Pitch Ball Grid Array (FBGA/FIBGA) Contact Diameter and Pitch Variations37                             | Figure 10-5  | Flux Height Measurement Gauges 58                                    |

| Figure 7-4  | JEDEC Package-on-Package (PoP)                                                                              | Figure 10-6  | Solder Balls After Paste Dip59                                       |

| riguie /-4  | Construction Variations                                                                                     | Figure 10-7  | Carrier with Prestacked Packages 59                                  |

| Figure 7-5  | Contact Redistribution at the Wafer<br>Level Provides a Method for Furnishing a                             | Figure 10-8  | Soldering Surface of Through-Mold Via (TMV) Balls                    |

|             | Uniform Array Format to Better                                                                              | Figure 10-9  | Ball Collapse                                                        |

|             | Accommodate Face-Down Mounting 38                                                                           | Figure 10-10 | Z-Height of a Package-on-Package                                     |

| Figure 8-1  | Two-Level Substrate with Embedded                                                                           |              | (PoP)60                                                              |

| E' 0.5      | Components                                                                                                  | _            | Joint Stand-Off Height (SOH)60                                       |

| Figure 8-2  | Ball Grid Array (BGA) Package Adopting<br>an Embedded-Component Substrate 41                                | Figure 10-12 | Package-on-Package (PoP) Die Gap60                                   |

| Figure 10-13 | Cavity and 3D Stencil61                                                                                                                  | Figure 10-38 | Comparing Two-Step Underfill Plus                                                                  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------------------------------------------------------------------------------------------|

| Figure 10-14 | Three-Dimensional (3D) Stencil with a Cavity Pocket on the Right61                                                                       |              | Mold Process (A) to the One-Step<br>Molded Underfill Packaged Die (B)72                            |

| Figure 10-15 | Slit-Metal Squeegee                                                                                                                      | Figure 10-39 | Void in Underfill Under Array-Configured Flip-Chip Die                                             |

| Figure 10-16 | Package-on-Package (PoP) Mounted into a Cavity                                                                                           | Figure 11-1  | Quality Document System                                                                            |

| Figure 10-17 | Jet Printing of Solder Paste for a 0.8-mm [0.031-in] BGA                                                                                 | Figure 13-1  | Acoustical Microscopy (AM) Can Identify Voids, Delamination and Cracks 80                          |

| Figure 10-18 | Multiple-Deposit Jet Printing for Customized Deposit Volumes                                                                             | Figure 13-2  | 3D Submicron X-Ray Imaging Distinctly Identifying Solder Bridging 80                               |

| Figure 10-19 | 3D Jet Printing on Camera Module 62                                                                                                      | Figure 13-3  | $Die\text{-to-Silicon-to-Substrate Assembly} \ \dots \ 82$                                         |

| _            | Cavity Keep-Out Zone                                                                                                                     | Figure 13-4  | Semiconductor Package Decapsulation                                                                |

| Figure 10-21 | Multilevel Printed Board                                                                                                                 | Eigung 12 5  | System                                                                                             |

| Figure 10-22 | Avoiding Interference in Multilevel                                                                                                      | Figure 13-5  | Head on Pillow (HoP) Solder Process Defect                                                         |

| Figure 10-23 | Placement Design                                                                                                                         | Figure 13-6  | Poor Coalesce Between Sphere and Interposer Land83                                                 |

| Figure 10-24 | Capillary Flow of Liquid Epoxy Fully                                                                                                     | Figure 13-7  | Nonwetting Defect, Exhibiting the Effect of Excessive Oxidation 83                                 |

|              | Encapsulating and Stabilizing the Area Between Two Parallel Surfaces                                                                     | Figure 13-8  | Endoscopy Edge View of Solder Bridge<br>Between Ball Grid Array (BGA) Sphere                       |

| Figure 10-25 | Soldering Material in Package-on-Package (PoP) Assembly                                                                                  |              | Contacts                                                                                           |

| Eiguro 10 26 | (PoP) Assembly                                                                                                                           | Figure 13-9  | Bridging on Package-on-Package (Pop)84                                                             |

| _            | Board Stacking with Interposer                                                                                                           | Figure 13-10 | Defect Attributed to Oxide Contamination                                                           |

| Figure 10-28 | Low-Temperature Alloys with Liquidus<br>Temperatures Between 100 °C and                                                                  | Figure 13-11 | Comparison of Wetting Characteristics of Two Surface Finishes                                      |

|              | 200 °C and Which Do Not Contain Pb,<br>Cd or Au                                                                                          | Figure 13-12 | Incomplete Solder Reflow84                                                                         |

| Figure 10-29 | Mixed-Alloy BGA Solder Joint Formed                                                                                                      | Figure 13-13 | Missing Solder Ball                                                                                |

|              | with SAC Ball Soldered with Ductile Metallurgy BiSn Solder Paste66                                                                       |              | Tables                                                                                             |

| Figure 10-30 | Package-on-Package (PoP) With                                                                                                            | Table 4-1    | Through-Mold Via (TMV) Examples 12                                                                 |

|              | Overlapping Memory Balls 67                                                                                                              | Table 5-1    | Interposer Material Properties Comparison                                                          |

| Figure 10-31 | Package-on-Package (PoP) with Overlapping Memory Balls Viewed with 3D Laminography X-Ray                                                 | Table 7-1    | Plastic Ball Grid Array (PBGA) Contact Diameter and Pitch Variations36                             |

| Figure 10-32 | Head on Pillow (HoP) 3D Laminography Image                                                                                               | Table 7-2    | Fine-Pitch Ball Grid Array<br>(FBGA/FIBGA) Contact Diameter<br>and Pitch Variations                |

| Figure 10-33 | Tilted 2D X-Ray View of Through-Mold<br>Interconnect (TMI) Package-on-Package<br>(PoP) with Head on Pillow (HoP) Defect<br>on the Memory | Table 7-3    | Comparing Wafer-Level Ball Grid Array (WLBGA) Contact Pitch to Ball or Bump Contact Diameter Range |

| Figure 10-34 | AM Images of a 3D Devices with and without Acceptable Defects 69                                                                         | Table 9-1    | Typical Feature Sizes for High Density<br>Interconnect (HDI) Substrate                             |

| Figure 10-35 | Rework with Laser Soldering70                                                                                                            | Table 10-1   | Constructions, µm [mil]                                                                            |

| Figure 10-36 | Package-to-Printed Board Reinforcement                                                                                                   | Table 10-1   | Stand-Off Height (SOH) of 0.4-mm [0.016-in] Package-on-Package (PoP) With 200-µm Balls             |

| Figure 10-37 | Edge Dispensing of Underfill Material 71                                                                                                 |              | ,                                                                                                  |

January 2023 IPC-7091A

# Design and Assembly Process Implementation of 3D Components

### 1 SCOPE

This document describes the design and assembly challenges and ways to address those challenges for implementing 3D component technology. Recognizing the effects of combining multiple uncased semiconductor die elements in a single-package format can impact individual component characteristics and can dictate suitable assembly methodology. The information contained in this standard focuses on achieving optimum functionality, process assessment, end-product reliability and repair issues associated with 3D semiconductor package assembly and processing.

- **1.1 Purpose** Performance-driven electronic systems continue to challenge companies in search of more innovative semiconductor package methodologies. The key market driver for semiconductor package technology is to provide greater functionality and improved performance without increasing package size. The package interposer is the key enabler. Although glass-reinforced epoxy-based materials and high-density Cu interconnect capability will continue to have a primary role for array-configured packaging, there is a trend toward alternative dielectric platforms as well as toward combining multiple functions within the same die element. To address this movement, an increasing number of semiconductor die developed for advanced applications now require higher I/O with contact pitch variations that are significantly smaller than the mainstream semiconductor products previously in the market. For these applications, companies are developing interposer technologies that can provide interconnect densities far superior to organic-based counterparts.

- 1.1.1 Target Audience The target audiences for this standard are managers, design/process engineers and operators who deal with:

- Implementing 3D semiconductor packaging

- · Interposer, substrate and printed board design

- · Board-level assembly, inspection and repair processes

- **1.1.2 Intent** This standard intends to provide useful and practical information to those who are designing, developing or using 3D-packaged semiconductor components or those who are considering 3D package implementation. The 3D semiconductor package may include multiple die elements—some homogeneous and some heterogeneous. The package may also include several discrete passive SMT devices, some of which are surface mounted and some of which are integrated (embedded) within the components' substrate structure.

- **1.2 Classification** IPC standards recognize that electrical and electronic assemblies are subject to classifications by intended end-item use. Three general end-product classes have been established to reflect differences in manufacturability, complexity, functional performance requirements, and verification (inspection/test) frequency. It should be recognized that there may be overlaps of equipment between classes.

# **CLASS 1 General Electronic Products**

Includes products suitable for applications where the major requirement is function of the completed assembly.

## **CLASS 2 Dedicated Service Electronic Products**

Includes products where continued performance and extended life is required, and for which uninterrupted service is desired but not critical. Typically, the end-use environment would not cause failures.

### **CLASS 3 High Performance/Harsh Environment Electronic Products**

Includes products where continued high performance or performance-on-demand is critical, equipment downtime cannot be tolerated, end-use environment may be uncommonly harsh, and the equipment must function when required, such as life support or other critical systems.

- **1.3 Measurement Units** All dimensions and tolerances in this specification are expressed in hard SI (metric) units and bracketed soft imperial [inch] units. Users of this specification are expected to use metric dimensions. All dimensions  $\geq 1$  mm [0.0394 in] will be expressed in millimeters and inches. All dimensions  $\leq 1$  mm [0.0394 in] will be expressed in micrometers and microinches.

- **1.4 Use of "Lead"** For readability and translation, this document uses the noun lead only to describe leads of a component. The metallic element lead is always written as Pb.

- **1.5 Abbreviations and Acronyms** Periodic table elements are abbreviated in the standard. See Appendix A for full spellings of abbreviations (including elements) and acronyms used in this standard.

IPC-7091A January 2023

1.6 Terms and Definitions Other than those terms listed below, the definitions of terms used in this standard are in accordance with IPC-T-50.

**1.6.1 Die\*** Separated piece(s) of a semiconductor wafer that constitutes a discrete semiconductor or integrated circuit (IC). They are normally uncased and leadless forms of an electronic component.

- \*singular or plural

- 1.6.2 Electronic Element A bare die/wafer or discrete component (resistor, capacitor, inductor, transistor, diode, fuse, etc.) with metallized terminals or terminations ready for mounting. The element can be an IC or a discrete electrical, optical or microelectronic mechanical system (MEMS) element. Individual elements cannot be further reduced without destroying their stated function.

- **1.6.3** Interposer A material placed between two surfaces to provide electrical insulation, redistribution of electrical connections, mechanical strength and/or controlled mechanical and thermal separation between the two surfaces.

- **1.6.4 Substrate** The insulating material upon which a conductive pattern may be formed. (The base material may be rigid or flexible. It may be a dielectric or insulated metal sheet.) For this document, the term substrate refers to an interconnect platform fabricated from organic dielectric materials (rigid, flexible or a combination of rigid and flexible materials). Sometimes referred to as package substrate.

- **1.6.5 Electronic Package** An individual electronic element or elements in a container that protect the contents to ensure integrity and provide terminals to interconnect the container to an outer circuit. Package outline is generally standardized or meets guideline documents. A package may function as electronic, optoelectronic or MEMS, and it may include bioelectronic elements (e.g., sensors).

- **1.6.6 Electronic Module** A functional block that contains individual electronic elements and/or electronic packages to be used in a next-level assembly. An individual module may include an application-specific function or multiple electronic functions (e.g., optoelectronic, mechanical). The module typically provides protection of its elements and packages to ensure the required level of reliability.

- **1.6.7 Three-Dimensional (3D) Packaging** Three-dimensional (3D) integration of heterogeneous elements, using traditional interconnection processes, to achieve vertically configured interconnections.

- **1.7 Implementation Challenges** The next generation of 3D assembly has many implementation challenges, since the technology is complex and requires process expertise that may require foundries, outsourced semiconductor assembly and test (OSAT) providers and original design manufacturers (ODMs). There is no clear direction where 3D packages will be built, tested and assembled. The type of process to be used and the order of assembly and stacking is not defined and depends on the assembler's expertise.

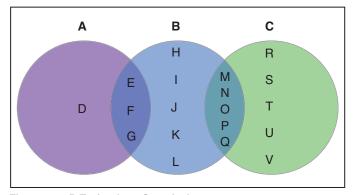

Figure 1-1 illustrates the technological complexity of 3D assembly.

As mobile electronics markets continue to see significant growth, there will be an increasing demand for product miniaturization and higher product performance expectation. Developers of personal communication and computing products, for example, have already adopted multicore processors. Furthermore, these high-performance processors will require greater memory bandwidth. To meet these market trends, manufacturers are predicting faster process capability and anticipate reduced power requirements to extend battery life. Next-generation semiconductor package solutions also are projected to be physically robust. While materials for organic-substrate-based applications will meet most commercial applications, more severe operating environments may require a more robust (nonorganic) base substrate material.

Industry may continue to rely on organic-based platforms for a majority of semiconductor packaging applications. When

Figure 1-1 3D Technology Complexity

- A Foundry

- B Outsourced semiconductor assembly and test (OSAT)

- C Original design manufacturer (ODM)

- D Wafer process

- E Wafer test known good die (KGD)

- Through-silicon via (TSV) interposer

- G Micro bumping

- H Package assembly

- I Wire bond

- Wafer-level packaging (WLP)

- K Package mold

- L Wafer bumping M – Package bumping

- N Die attach

- O 2.5D assembly

- P Underfill

- Q Prestacked

- R Printed board assembly

- S Package-on-package (PoP) assembly

- T Rework

- U Corner glue

- V System test