#### Presented at IPC Printed Circuits Expo® SMEMA Council APEX® Designers Summit 04

#### The CAD Library of the Future

#### Tom J. Hausherr, C.I.D.+ San Diego, CA

#### Abstract

The electronics industry is constantly growing and introducing new technology sometimes faster than we can keep up with. This paper reviews one of the single most important, but sometimes overlooked or taken for granted, aspects of the electronics industry, The CAD Library Land Pattern.

Every electronic component requires a solder land pattern for PCB layout. The solder pattern can be placed into two categories.

- Meet all the industry standard requirements for the sole purpose of electronic product creation automation.

- Fail to meet the industry standard requirements and create electronic product creation chaos.

This paper will describe the industry standard requirements so EE Engineers, PCB Designers and PCB Assembly Lines can fully automate their processes, become more efficient and productive. This of course will lead to faster product development cycles, reduction in overall costs, and reduction in error rate. If correctly implemented, you can eventually achieve elimination of duplication.

On the other hand, if you do not follow standardization, there are companies that exist that will gladly take your money to verify whether the land patterns you created are correctly built. But, even if the component will fit the land pattern that you created, there are still other factors, like "Zero Component Rotation", that must be considered to automate the manufacturing process.

The CAD Library of the Future will be a "One World Standard Library" that will be accepted by the electronics industry to eliminate duplication of effort and automate all of the engineering, design layout, manufacturing and assembly processes.

The following pages explain the criteria needed to create "The CAD Library of the Future". But first, let's meet the key players whose goal is to standardize the electronics product development industry.

#### **Electronic Standard Organizations**

#### Standards Organizations

Standard component package outlines come from industry standard organizations that specialize in component packaging data and standardization of documents and publications. (See Figure 1.)

These organizations include JEDEC, EIA, IEC, NIST, IPC, ANSI, EIAJ and JEITA

**Figure 1 – Industry Standard Organizations**

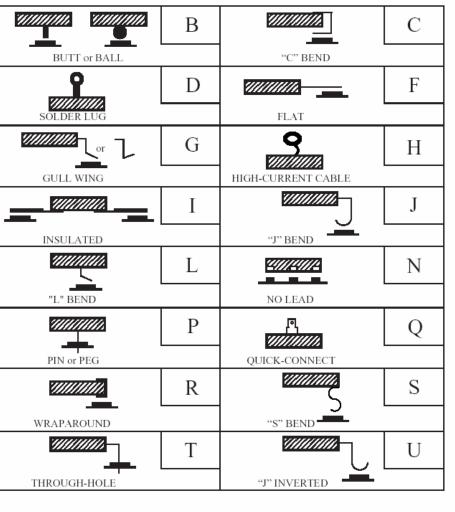

#### Component Lead Forms Standard JEDEC Component Leads

|              | В  |                    | 0         |

|--------------|----|--------------------|-----------|

| BUTT or BALL |    | "C" BEND           |           |

| <b>P</b>     | D  |                    | F         |

| SOLDER LUG   |    | FLAT               |           |

|              | G  | <b>9</b>           | H         |

| GULL WING    |    | HIGH-CURRENT CABLE |           |

|              | I  |                    | J         |

| INSULATED    |    | "J" BEND           |           |

|              | L  | 2///2///2          | N         |

| "L" BEND     | 25 | NO LEAD            | 16        |

|              | Р  | <b>R</b>           | 0         |

| PIN or PEG   | 27 | QUICK-CONNECT      | 62<br>152 |

|              | R  | <u>siiiiiiiii</u>  | S         |

| WRAPAROUND   | 25 | "S" BEND           | 108       |

|              | Т  |                    | , U       |

| THROUGH-HOLE |    | "J" INVERTED       | Ĺ         |

The Figure 2 illustrates all the different component leads that must solder to a PCB board.

Figure 2 – Different Component Leads

#### Solder Joint Tolerance

#### Component Lead Space Tolerance

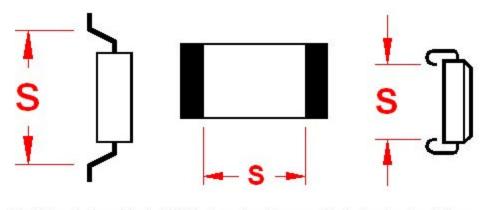

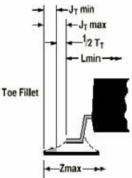

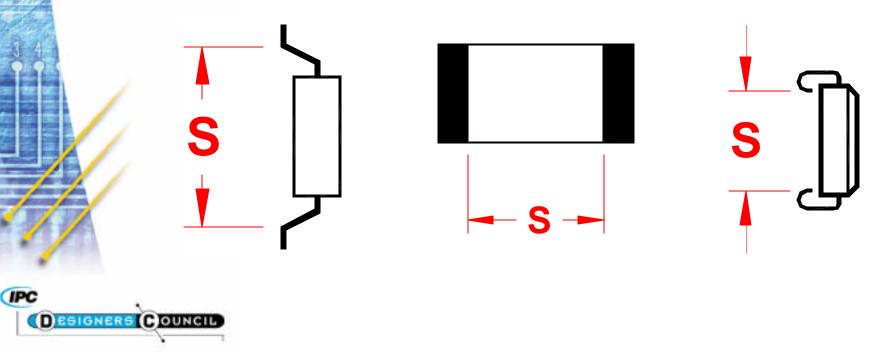

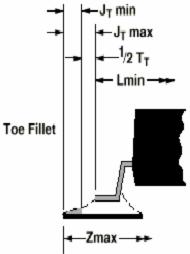

This Solder Joint Tolerance is for the inside dimension between the component terminal. It is normally represented by the "S" symbol. See the pictures below as a reference. (See Figure 3.)

The "S" dimension is used to calculate the inside spacing of Component Terminal Leads and has Minimum & Maximum values referred to as the "S" Tolerance. The "S" dimensional tolerance has a direct affect on the Toe and Heel values which in turn affect the overall pad length.

The "S" dimension is used to calculate the inside spacing of Component Terminal Leads and has Minimum & Maximum values referred to as the "S" Tolerance. The "S" dimensional tolerance has a direct affect on the Toe and Heel values which in turn affect the overall pad length.

#### Figure 3 – "S" Dimension

#### Land Pattern Pad Length Tolerance

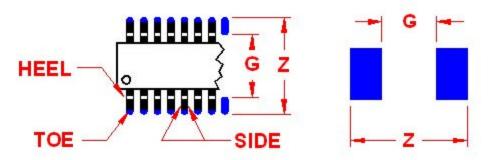

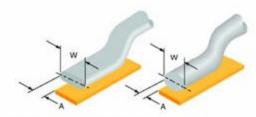

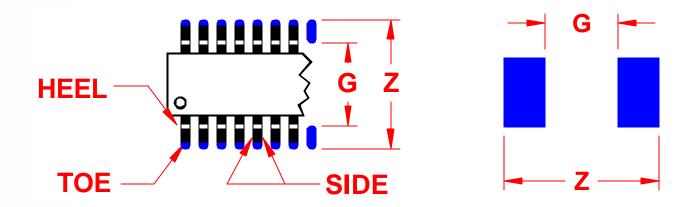

The "G" dimension is used to calculate the minimum and maximum inside spacing of the solder pad. The "Z" dimension is used to calculate the minimum and maximum outside spacing of the solder pad. See pictures.

The "G" and "Z" values are used to determine the maximum and minimum values of the pad length. They take into consideration the component terminal length tolerance, the Toe value (the pad size on the outside of the component terminal) and the Heel value (the pad size on the inside of the component terminal). (See Figure 4.)

The "G" and "Z" values are used to determine the maximum and minimum values of the pad length. They take into consideration the component terminal length tolerance, the Toe value (the pad size on the outside of the component terminal) and the Heel value (the pad size on the inside of the component terminal).

Figure 4 – "G" and "H" Values

The CAD Library of the Future will use Solder Joint Tolerance data to determine the land pattern pad size

#### Solder Joint Analysis Solder Joint Toe, Heel and Side Goal

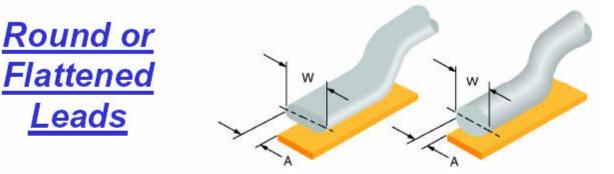

The Figure 5 provides an example of the typical Gull Wing component lead Solder Joint Goal

Round or flattened (coined) leads (unit: mm)

| Land pattern<br>characteristics | Maximum<br>Level 1 | Median<br>Level 2 | Minimum<br>Level 3<br>0.2<br>0.2 |  |

|---------------------------------|--------------------|-------------------|----------------------------------|--|

| Toe-land protrusion             | 1,0                | 0.65              |                                  |  |

| Heel-land protrusion            | 0,5                | 0,35              |                                  |  |

| Side-land protrusion            | 0,1                | 0,1               | 0.1                              |  |

| Courtyard excess 0,5            |                    | 0,25              | 0.05                             |  |

| Round-up factor                 | Nearest 0.5        | Nearest 0.5       | nearest 0.05                     |  |

Figure 5 – Typical Gull Wing Component Lead Solder Joint

The Figure 6 provides an example of the typical Gull Wing component lead Solder Joint Goal

Cylindrical end cap terminations (MELF) (unit: mm)

| Land pattern<br>characteristics | Maximum<br>Level 1 | Median<br>Level 2 | Minimum<br>Level 3 |  |

|---------------------------------|--------------------|-------------------|--------------------|--|

| Toe-land protrusion             | 1.0                | 0.4               | 0,2                |  |

| Heel-land protrusion            | 0,2                | 0,1               | 0,0                |  |

| Side-land protrusion            | 0.2                | 0,1               | 0,0                |  |

| Courtyard excess                | rtyard excess 0,5  |                   | 0,05               |  |

| Round-up factor                 | Nearest 0,5        | Nearest 0,5       | Nearest 0,05       |  |

Figure 6 – Typical Gull "Wing Component

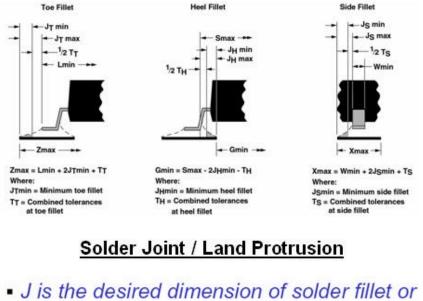

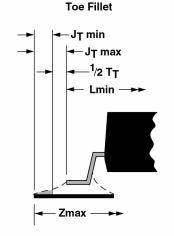

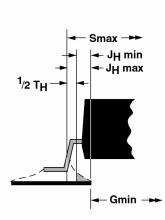

Figure 7 provides a graphical representation of the Gull Wing component lead to calculate the Toe, Heel and Side minimum and maximum values.

J is the desired dimension of solder fillet or land protrusion;

J<sub>t</sub> is the solder fillet or land protrusion at toe;

J<sub>h</sub> is the solder fillet or land protrusion at heel;

J<sub>s</sub> is the solder fillet or land protrusion at side;

### Figure 7 – Representation of the Gull Wing Component Lead to Calculate the toe, Heel and Side Minimum and Maximum Values.

The CAD Library of the Future will use Solder Joint Analysis to determine the land pattern pad size.

#### **Manufacturing Tolerance**

#### Fabrication Tolerances

When calculating a land pattern pad size, a fabrication tolerance must be applied to compensate for the etch-back of every feature on the outer layer of a PC board. To control the line width for impedance calculations, the PC board manufacturer might widen the trace width to compensate for the etch-back process, but they do not widen every surface mount pad size to compensate for the etch-back process.

A fabrication tolerance is added into the pad size equation. The standard fabrication tolerance is  $\pm 0.05$ mm.

#### Assembly Tolerances

The assembly process also has a manufacturing tolerance that must be considered. The standard assembly tolerance allowance is  $\pm 0.05$ mm.

#### **Component Terminal Tolerances**

Every component terminal lead has a manufacturing tolerance that the component manufacturer must hold to. The larger the component lead tolerance minimum and maximum values, the longer the land pattern pad must be to compensate for the component manufacturing tolerance.

Figure 8 shows the mathematical formula for calculating the Z, G and X dimensional values by taking into consideration the Component, Fabrication and Assembly Tolerances.

- $Z_{max} = L_{min} + 2J_T + \sqrt{C_L^2 + F^2 + P^2}$   $G_{min} = S_{max} 2J_H \sqrt{C_L^2 + F^2 + P^2}$   $X_{max} = W_{min} + 2J_S + \sqrt{C_L^2 + F^2 + P^2}$

- where

- Z is the overall length of land pattern;

- > G is the distance between lands of the pattern;

- > X is the width of land pattern;

- **Figure 8 Land pattern Equations**

The CAD Library of the Future will use Fabrication, Assembly and Component Lead tolerances

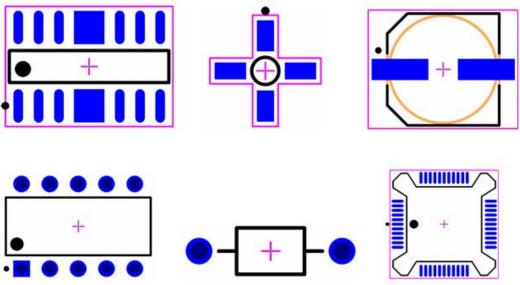

#### **Zero Component Rotation – Jep95**

#### Pick & Place Machine Tape & Reel Rotation Requirements

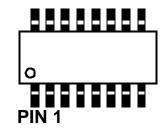

The Component Zero Rotation relates to the Pick & Place machine tape and reel and component tubes. The rotation of the actual component in the tube or tape & reel is referred to as the Zero Rotation for the CAD Library part and how it should be built in the CAD library. All CAD Library parts should be built in the CAD system in the same rotation that the component is packaged in the tape and reel or assembly feeder tube.

The JEDEC JEP95 specification is the industry guideline for component packaging information.

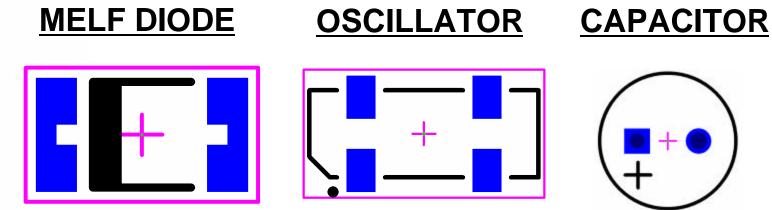

This is a list of the most commonly used parts in the world today and their correct Zero Rotation: (Figure 9)

- 1) Chip Capacitors, Resistors and Inductors (RES, CAP and IND) Pin 1 on Left

- Molded Capacitors and Inductors (Tantalum Capacitors) Pin 1 (Positive) on Left 2)

- Precision Wire-wound Inductors Pin 1 on Left 3)

- 4) MELF Resistors and Diodes Pin 1 (Cathode) on Left

- 5) Aluminum Electrolytic Capacitors Pin 1 (Positive) on Left

- 6) SOT Devices (SOT89, SOT143, etc.) Bottom Left

- TO 252/268 Devices Bottom Left 7)

- 8) Small Outline Gullwing ICs (SOIC, SOP, TSOP, etc.) Bottom Left

Or for TSSOP packages with leads protruding from short side of body (Whenever the component body width is longer than the component body length) Left Top:

- 9) Small Outline J Lead ICs (SOJ) Bottom Left

- 10) Quad Flat Pack ICs (PQFP, SQFP) Bottom Left

- 11) Ceramic Quad Flat Packs (CQFP) Left Top

- 12) Ceramic Flat Packs (CFP) Bottom Left

- 13) Plastic Leaded Chip Carriers (PLCC) Left Center

- 14) Leadless Chip Carriers (LCC) Top Center

- 15) Quad Flat No-Lead ICs for QFNS & QFNRV (Vertical) Left Bottom

OFNRH (Horizontal) Outlines - Top Left:

16) Ball Grid Arrays (BGA) - Bottom Left

Figure 9 – Part Zero Rotation

The CAD Library of the Future will use the JEDEC JEP95 publication Zero Component Rotations

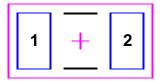

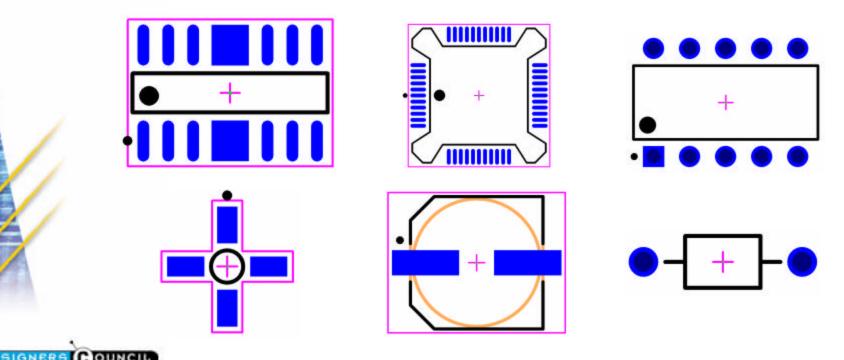

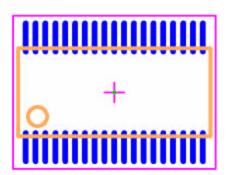

#### Land Pattern Origin CAD Library Part Origins

The land pattern origin is the component "Center of Gravity" so in most cases it's the Center of the library part. An example of where it's not the center is the DPAK or TO-252 component.

The land pattern origin is the zero point in which all the features of the land pattern are derived. The origin is also the center of rotation. The point in which the land pattern rotates around is the Land Pattern Origin.

Before SMT parts came into existence, the common land pattern origin for through hole parts was Pin 1. The main reason for this was a convenience to the PCB designer to keep the component pins on a common grid to make the routing phase of the PCB design layout easy.

When the PCB designer provided X Y coordinate data to the assembly shop, the engineers at the assembly shop had to invent calculators for the various through hole devices that relocated the part origin from pin 1 to the center of the part.

Today with SMT and Through Hole mixed technology and with the need to streaml ine and automate the assembly process, all land origins should be located in the part center. The only exception to this rule would be components or connectors that absolutely require hand assembly. Then the PCB designer can select the land pattern origin to whatever makes their job easier.

A good feature to add to the CAD library land pattern is a cross hair placed on a documentation layer so that it is visible to the PCB designer. This is a part placement aid. When the PCB Designer selects a component to move it, most CAD tools will make the part origin jump to wherever the cursor is. This is very annoying when you're fine-tuning a part placement and your goal is just to tweak the placement. If you can visually see the cross hair on the origin, you can select the part at the cross hair location and the part will not jump.

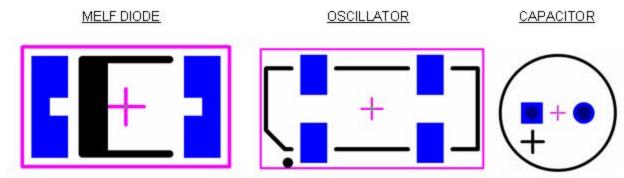

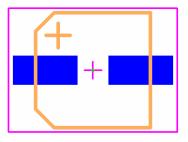

#### Sample Pictures of Land Pattern Origins

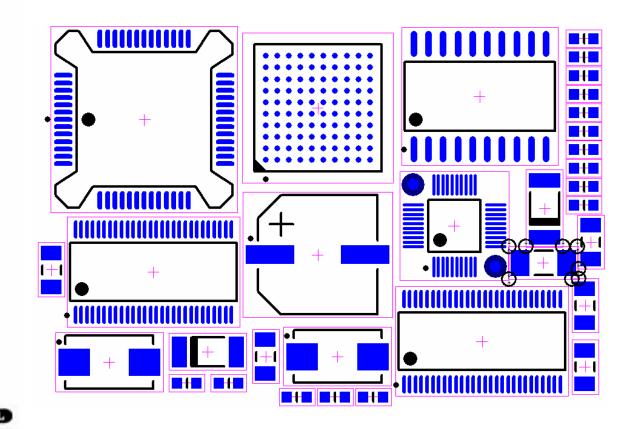

Figure 10 shows the sample pictures of land pattern origins.

Figure 10 – Pictures of Land Pattern Origins

#### Placement Courtyard

SMT Placement Courtyard

The placement courtyard was introduced by IPC in the IPC-SM-782 Surface Mount Design Land pattern Standard in 1987.

The primary use of the placement courtyard was to provide the PCB designer a guideline for placing land patterns next to each other with enough room to compensate for component tolerances.

Courtyard outlines are used to insure that all parts will fit, but they do not compensate for assembly machine heads and manufacturing allowances. Each assembly manufacturer has there own unique processes that require various allowances. Placement Courtyards are not meant to touch each other or overlap. They should have a space gap in-between them so when the PCB Designer runs a Design Rule Check for Body-to-Body clearance, there should be "No Errors Found".

The standard courtyard line width is 0.1mm and it's placed on a layer designated by the CAD vendor. The Placement Courtyard is used as a CAD visual graphic aid for part placement and never post processed.

#### Sample Part Placement

The placement of parts shown in Figure 12 has a design rule of 0.05mm Body-to-Body. There is one component that violates to Body-to-Body spacing rule and produces error markers when a Design Rule Check is run. (See Figure 11.)

Figure 11 – Error Markers for Body-to-Body Spacing Violations

#### Land Pattern Courtyard Determination

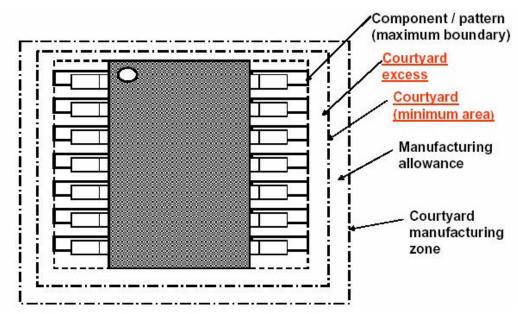

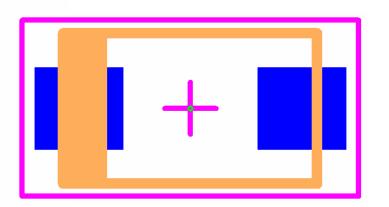

The Figure 12 shows the Component Boundary, the Minimum Courtyard Excess and the Manufacturing Allowance.

Figure 12 – Land pattern Courtyard Determination

It's the Courtyard Manufacturing Zone that is critical for the assembly process. This is the Body-to-Body clearance that you set in your Design Rules for Design Rule Checking. The size of the manufacturing tolerance must come from the assembly shop that is going to be used to populate the parts on the PC Board. Every assembly shop has different assembly tolerances, but the average is 0.1mm.

The assembly process makes it very difficult to determine placement courtyards for through hole components. It's easy to determine SMT to SMT and even Through Hole to Through Hole, but SMT to Though Hole gets complex, especially when placing Through Hole parts on the Top Side and SMT parts on the bottom side. Since Through Hole parts require holes that go all the way through the PC Board, the Through Hole part Top Side courtyard would be different than the bottom side courtyard due to the wave solder process used to solder Through Hole component leads. If wave solder is used for the Through Hole component leads, the SMT parts mounted on the bottom side must have a 5mm clearance between the edge of the Through Hole pad and edge of the SMT pad. If a selective wave is used there is a different tolerance between the pads depending on the assembly shop requirements.

Therefore, building in placement courtyards for through hole parts is almost impossible due to too many variables. A PCB designer must use common standard rules provided by the assembly shop when performing the part placement. The assembly shop should always approve the part placement prior to routing any traces on the board. This is an official check point that must not be avoided.

#### Silkscreen Outline and Polarity

#### Silkscreen Outlines

Silkscreen outlines are used for cosmetic purposes only and are really not required by manufacturing.

Most CAD land pattern silkscreen outlines are not representative of the true component outline. Silkscreen outlines must avoid the exposed copper pad by 0.4mm for maximum clearance 0.3mm nominal or 0.25mm minimum.

The standard acceptable line width for silkscreen outlines is 0.2mm.

The silkscreen can be drawn by the PCB designer very complex to illustrate their creative talent or very simple. In the end, it really doesn't matter because you can only see it when the physical PC board passes between the fabrication facilities to the assembly shop. Once the parts are assembled, all the silkscreen outlines are covered up and cannot be seen.

The silkscreen originated from the hand tape days. Back in the 1970's PC boards did not have silkscreen outlines. Assembly drawings were created using rectangles and circles. Some PCB designers decided the assembly drawing would look good if it appeared on the PC board and the silkscreen was born.

Now, most boards have part placements that are so tight that there's no room for silkscreen outside the part. It's my opinion that with a one world standard library and full machine automation that the silkscreen will be a thing of the past. It's interesting to note that on PC boards that go into outer space purposely do not have silkscreen to reduce the weight of the product.

When PCB designers start to use all the principles discussed in this outline, the manufacturing assembly process can be fully automated. The Cad Library of the Future will not require the use of silkscreen outlines.

#### Silkscreen Polarity Markings

Some assembly shops or test engineers who are debugging a prototype might require silkscreen Polarity Markings. Silkscreen Polarity Markings are primarily used to illustrate the "Positive" terminal of a two-pin component. Polarity Markings are also used when there is a potential for inverting the part placement in the assembly process that would result in a malfunction of the component.

The term Polarity Marking came from its use to identify the Positive Pin on a "Polarized" capacitor. But polarity marking is also used on diodes to indicate the Cathode Pin. It's also used on connectors to illustrate the Pin 1 location. Figure 13 shows some samples of Silkscreen Polarity Markings.

Figure 13 - Samples of Silkscreen Polarity Markings

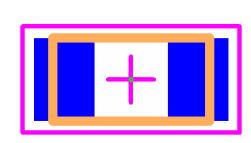

#### Assembly Outline and Polarity Mark Assembly Drawing Outlines

The assembly drawing outline should represent the maximum outline of the component body. Unlike the silkscreen outline which has to be created to avoid solder pads (a fake component outline); the assembly outline only gets placed on an assembly drawing that goes to the assembly shop. There is no need to fake this outline.

Assembly outlines can be created with complex drawings to illustrate the actual physical component features or with a simple rectangle. It makes no difference to the assembly shop that has to interpret the assembly drawing. Drawing complex shapes for the assembly outline shows off the PCB designer's artistic creativity, but once the PC Board goes into production, it makes no difference because the assembly drawing is never used again. The CAD Library of the Future will have 1:1 scale component outlines in the assembly drawing.

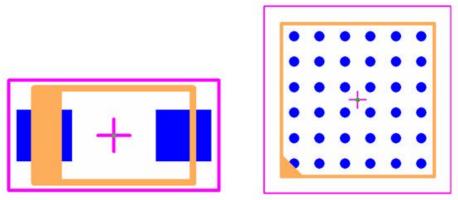

Figure 14 shows some sample assembly drawing component outlines in relationship to the solder pad.

Figure 14 - Sample Assembly drawing component Outlines in Relationship to the Solder Pad

#### Assembly Polarity Marking

The assembly Polarity Marking is sometimes totally different than the silkscreen Polarity Marking because the silkscreen must avoid touching the solder pad. Unlike the silkscreen, the assembly drawing can illustrate robust polarity markings to insure that the component is inserted with the correct rotation.

Figure 15 shows some sample assembly drawing component Polarity Markings in relationship to the solder pad.

Figure 15 - Sample Assembly Drawing Component Polarity Markings in Relationship to the Solder Pad

#### Padstacks

#### Surface Mount Padstack

The surface mount component padstack consists of a solder pad, solder mask and solder paste. We've already discussed the creation of the pad size. The solder mask and paste mask size is typically the same as the pad size.

Solder Mask - We allow the PC Board manufacturer expand the solder mask size according the rule technology that the PCB designer used to design the PCB layout. If the design layout had a trace/space rule setting of 0.3mm (0.012") then the manufacture could expand the solder mask size larger than if the design layout had a trace/space rule of 0.1mm (0.004").

In the past PCB designers had a strict rule that the PC Board manufacturers not modify their Gerber data. But with today's CAM technology, board manufacturers often have more advanced design rule checking features than our CAD tools do. It's OK to let the board manufacturer adjust the solder mask size to accommodate their manufacturing equipment and solder mask application technique. It's probably better that PCB designers let the manufacturers do their job and to not try guess what the manufacturer needs.

The most important aspect is that all solder mask sizes be built in the padstack 1:1 scale so that the manufacturer can globally oversize all pads with the same oversize. All Solder Mask sizes are in increments of 0.05mm.

Solder Paste – We allow the stencil maker to oversize the solder paste to match the specifications of the assembly shop that the paste mask stencil is being made for. It is important that the Solder Paste size in the padstack be the same size as the pad to make the stencil creation process easy. If we make adjustments for BGA pad sizes or other SMT components, the stencil maker does not know this. It's much better to tell the solder paste stencil maker that all the pad size data is 1:1 scale to the Solder Paste data.

#### Through Hole Padstack

The Through Hole Padstack is much more complex than the Surface Mount Padstack because it contains a drill size that goes all the way through the PC Board.

This is what a typical Through Hole Padstack is built like:

- Top Solder Mask

- Top Pad

- Inner Layer Pad

- Plane Anti-pad

- Plane Thermal Relief

- Bottom Pad

- Bottom Solder Mask

- Drilled Hole

Solder Mask – The rule mentioned above is applicable to the Through Hole Padstack.

Pad Size – The Pad Size is determined by two factors. 1. It is at least 0.25mm (0.010") larger than the Drilled Hole size. 2. It is capable of handling the electrical current of the component lead. The larger the component lead, the larger the hole size, the more potential for high current. Component manufactures do not make large component lead sizes unless they are intended to withstand a particular electrical current. The Pad Size must also be able to withstand that same current or it will become a fuse point that has the potential of heating up past the melting point temperature of the prepreg that the pad is fused to.

Anti-pad – The Power Plane Anti-Pad is the copper clearance around the drilled hole on an inner layer power or ground plane. The Anti-pad size is determined by two factors. 1. The PC Board manufacturer requires the anti-pad size to be at least a minimum of 0.5mm (0.020") larger than the drilled hole and a nominal size if 0.6mm (0.024") larger than the drilled hole. 2. The EE Engineer does not want you to make the anti-pad any larger than the PC Board manufacturers nominal size because the anti-pad = anti-copper or the removal of copper from the power or ground plane. It is very important in today's high speed design layouts that every critical signal has a clean return path. If the plane anti-pads are created too large the signal traces pass over areas void of copper creating signal integrity problems. All Anti-pad sizes are in increments of 0.05mm.

Thermal Relief – The Power Plane Thermal Relief has five attributes. Thermal Relief's have an outside diameter, an inside diameter, a spoke width, a spoke rotation and 2 or 4 spokes. The Outside Diameter is typically the same size as the Anti-pad. The inside diameter is typically 80% less than the outside diameter. The spoke width is typically 4 times smaller than the outside diameter with 4 spokes or 3 times smaller than the outside diameter with 2 spokes. The spoke rotation is normally 45 degrees with 4 spokes. All Thermal Relief feature sizes are in increments of 0.05mm.

Drilled Hole – The Drilled Hole size is typically 0.3mm (0.012") larger than the longest portion of the component lead size and rounded up to the nearest 0.05mm (0.002"). All Drill Hole sizes are in increments of 0.05mm.

Table 1 is the most commonly used Through Hole component leads.

| Sizes for | Plated Thro      | ough Hole Co   | omponen      | t Padstacks     |                             |                       |                       |                    |                  |

|-----------|------------------|----------------|--------------|-----------------|-----------------------------|-----------------------|-----------------------|--------------------|------------------|

| All dime  | ensions are d    | iameters in r  | nm           |                 |                             |                       |                       |                    |                  |

| Lead<br>? | Finished<br>hole | Mounted<br>Pad | Inner<br>Pad | Opposite<br>Pad | Solder<br>Mask<br>Top - Bot | Assembly<br>Top & Bot | Plane<br>Anti-<br>Pad | Thermal<br>ID x OD | Thermal<br>Spoke |

| 0.10      | 0.40             | 0.70           | 0.70         | 0.70            | 0.70                        | 0.70                  | 1.15                  | 0.9x1.15           | 0.35             |

| 0.15      | 0.45             | 0.75           | 0.75         | 0.75            | 0.75                        | 0.75                  | 1.20                  | 0.95x1.2           | 0.35             |

| 0.20      | 0.50             | 0.85           | 0.85         | 0.85            | 0.85                        | 0.85                  | 1.25                  | 1x1.25             | 0.35             |

| 0.25      | 0.55             | 0.95           | 0.95         | 0.95            | 0.95                        | 0.95                  | 1.35                  | 1.05x1.35          | 0.35             |

| 0.30      | 0.60             | 1.00           | 1.00         | 1.00            | 1.00                        | 1.00                  | 1.40                  | 1.1x1.4            | 0.40             |

| 0.35      | 0.65             | 1.10           | 1.10         | 1.10            | 1.10                        | 1.10                  | 1.45                  | 1.15x1.45          | 0.40             |

| 0.40      | 0.70             | 1.15           | 1.15         | 1.15            | 1.15                        | 1.15                  | 1.50                  | 1.2x1.5            | 0.40             |

| 0.45      | 0.75             | 1.25           | 1.25         | 1.25            | 1.25                        | 1.25                  | 1.55                  | 1.25x1.55          | 0.40             |

| 0.50      | 0.80             | 1.35           | 1.35         | 1.35            | 1.35                        | 1.35                  | 1.60                  | 1.3x1.6            | 0.40             |

| 0.55      | 0.85             | 1.40           | 1.40         | 1.40            | 1.40                        | 1.40                  | 1.65                  | 1.35x1.65          | 0.40             |

| 0.60      | 0.90             | 1.50           | 1.50         | 1.50            | 1.50                        | 1.50                  | 1.70                  | 1.4x1.7            | 0.40             |

| 0.65      | 0.95             | 1.60           | 1.60         | 1.60            | 1.60                        | 1.60                  | 1.75                  | 1.45x1.75          | 0.40             |

| 0.70      | 1.00             | 1.65           | 1.65         | 1.65            | 1.65                        | 1.65                  | 1.80                  | 1.5x1.8            | 0.40             |

| 0.75      | 1.05             | 1.75           | 1.75         | 1.75            | 1.75                        | 1.75                  | 1.90                  | 1.55x1.9           | 0.40             |

| 0.80      | 1.10             | 1.85           | 1.85         | 1.85            | 1.85                        | 1.85                  | 1.95                  | 1.6x1.95           | 0.40             |

| 0.85      | 1.15             | 1.90           | 1.90         | 1.90            | 1.90                        | 1.90                  | 2.00                  | 1.65x2             | 0.40             |

| 0.90      | 1.20             | 2.00           | 2.00         | 2.00            | 2.00                        | 2.00                  | 2.05                  | 1.7x2.05           | 0.40             |

#### **3D** Component Outline Component 3D Modeling

Every CAD tool has a different approach to handling 3D Models of component data. Some are much more elaborate than others.

The CAD tool that I use is PADS-PowerPCB and I own the IDF translator that is capable of extracting "Closed Polygon" data from the land pattern parts.

The PADS IDF translator has a requirement that the component outline must be a closed polygon and it must be on a layer that does not contain any other graphic features, just the component outline.

So in the PADS tool we use Layer\_25 to construct a closed polygon of the maximum body size of the component outline.

The line width for the component outline should be "Zero Width" but PADS does not have that feature so we a 1 micron line width.

The Geometry Height of the component is stored in a Part-Type attribute called Geometry.Height.

The unit structure for the Geometry Height attribute is just a number for mil units. It must have "mm" following the number if the units are metric and the number must be followed by the "sign if the value is in inches.

When you run the IDF program using PADS File/Export, the program has a layer input field that the user enters and the program looks at all the library parts for the existence of a closed polygon on that layer.

If no closed polygon exists, the program will search through all the layers trying to find a closed polygon that is isolated on a layer.

If you do not have a closed polygon on an isolated layer with no other graphics, the program automatically draws a rectangular outline around the outside perimeter of the part extents and uses that shape to portray the 3D Model.

The IDF program produces two files, .emn and .emp which are imported directly into PRO-E for 3D Model illustration. SolidWorks has a translator that can be used to import the same data in their CAD tool.

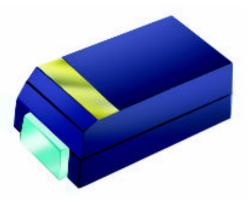

The CAD Library of the Future will have 3D Model attributes built into every land pattern to use as a mechanical drafting aid for the reduction of errors in product packaging. (See Figure 16.)

Figure 16 – 3D Model

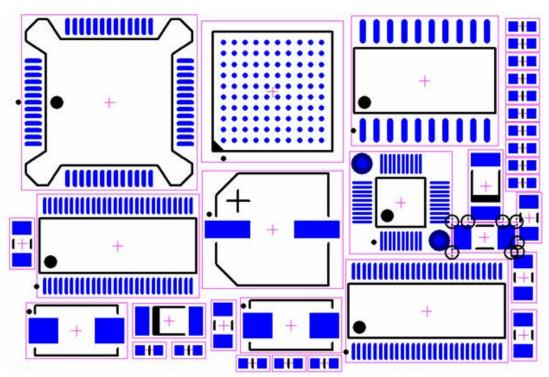

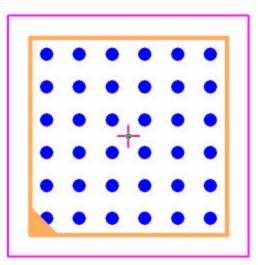

#### IPC-7351 3-Tier Library System The IPC-7351 3-Tier Construction

The unique aspect regarding IPC-7351 specification is the 3-Tier CAD Library System.

Different electronic products have different requirements for reliability, maintainability and board density.

With the 3-tiered library construction concept you can generate land patterns to meet those different requirements by varying the pad and courtyard dimensions.

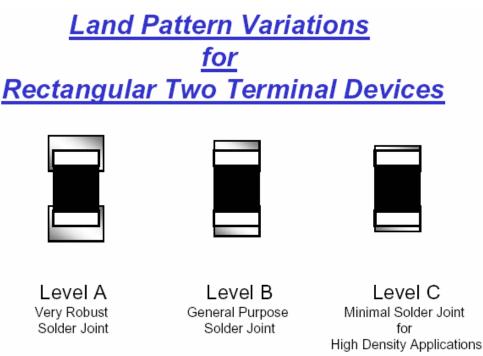

Here are the three different tiers and how and when you should use them: (Figure 17)

Most - for boards that are subjected to high shock/vibration or are involved in life support such as automotive, aerospace, medical applications and military products

IPC Performance Level A "High Reliability Electronic Products."

Nominal - for boards that are in devices that require only average dependability such as consumer applications, computers, appliances and home entertainment systems

IPC Performance Level B "Dedicated Service Electronic Products"

Least - for boards that are thrown away if they break or need service such as cell phones, Palm Pilots, toys, PCMCIA boards or very dense boards.

IPC Performance Level C "General Electronic Products"

Figure 17 – Land pattern Variations for Rectangular Two Terminal Devices

The Cad Library of the future will use the 3-Tier construction approach

#### **IPC-7351** Specification

In addition to the 3-Tier specification, the electronics industry and the IPC-7351 specification will also standardize on the following CAD Land Pattern features:

- Correct pad size that allows for manufacturing tolerances

- Correct pad spacing the allows for accurate solder joints

- Correct Zero Rotation for pick and place machine automation

- A good land pattern naming convention that standardizes the process of building schematic symbols with a link to the correct CAD Land Pattern

- Part Placement Courtyard boundaries

- The correct land pattern origin for pick and place machines

- Silkscreen and exposed copper allowance

#### IPC-7351 Free Library Construction for PADS

PCB Libraries builds all "IPC-7351 Standard SMT Library Parts", free of charge, for PADS-PowerPCB<sup>TM</sup> V4 & V5. One of our goals is to build every standard part in the world and offer it for free download on <u>www.PCBLibraries.com</u> to every PADS<sup>TM</sup> user.

Here is a list of what PCB Libraries considers standard SMT parts:

- BGA

QFP

TOFP

SOIC

- TSOP

- SOJ

- MELF

- Molded Diodes

- Tantalum Capacitor

- Molded Resistor

- All JEDEC Standard Components

#### IPC-2581 Neutral Cad Format Electronic Product Hardware Design Automation

True electronic product hardware design automation cannot be achieved until the electronics industry creates and accepts two basic fundamental standards:

Chip Resistor, Capacitor

- 1. A guideline specification for all CAD Land Pattern Library creation (IPC-7351) mentioned in chapter 15.

- 2. A neutral CAD format that is universal and can be interpreted (Imported and exported) by every CAD tool and manufacturing tool (IPC-2581). In order to fully explain the importance of the IPC-2581, we first must identify the key players in the electronics industry.

#### The Electronics Industry

Who and what is the "Electronics Hardware Industry"?

It's a combination of the following groups:

- Electronic Engineers

- PCB Designers

- PCB Manufacturers

- PCB Assembly Shops

- CAD Vendors

- CAM Vendors

- Standards Groups

- Component Manufacturers

A standard CAD Land Pattern Library is at the center of electronic product development automation because it has a direct affect with all the above groups.

#### PCB Design Engineering:

All EE engineers require a standard land pattern name that links with their schematic symbol to automate the process of providing the PCB Designer with accurate data. An engineer that has a good schematic library that is linked to the correct IPC-7351 Land Pattern data, can reduce both the engineering design cycle and the potential error rate.

#### PCB Design Layout:

All PCB Designers need a CAD Land Pattern Library to perform their job function. The better the CAD Library the better the PCB. It is a fact that a good and complete CAD Library can reduce the PCB Design Layout process by as much as 20%.

#### PCB Fabrication:

The CAD Land Pattern library has built in features that drive the PCB manufacturing processes. 80% of all manufacturing errors and/or cleanup are directly related to poor CAD Library construction. Some of these items include: inadequate inner layer plane anti-pads (too large or too small), silkscreen outlines that intersect with exposed copper pads, inadequate annular rings on pads and many other items that could be avoided with a good CAD Library.

#### PCB Assembly:

The CAD Land Pattern library has built in features that drive the PCB assembly process. 80% of all assembly problems occur from errors that are related to poor land pattern construction. Some of these items include: Incorrect hole size for the component lead, incorrect pin pitch for the pad spacing, SMT pads that are too small or too large, poor solder mask allowances, incorrect Zero Rotation for pick and place machines, unknown component origins, non-standard land pattern naming conventions,

QFN SOT

SQFP

SOP

• 501

and

•

- CFP

- Aluminum Electrolytic Capacitors

- Wire Wound Inductor

- TO Packages

CQFP

TSSOP

PLCC

Inductor

Molded Inductor

**CWR06** Capacitors

LCC

inadequate placement courtyards that allow for component and manufacturing tolerances and many other things that have a direct affect on the assembly automation process.

#### PCB CAD Vendors:

The CAD vendors historically have provided CAD Libraries with their tools however a major consensus has reveled that the majority of all PCB designers do not use the stock vendor CAD library for several reasons. Normally the CAD vendor cannot keep up with the component industry and their libraries get old and useless. The CAD vendor library does not come with any documentation so it leaves the PCB designer guessing on which library part to use. The day has come when CAD vendors must make a decision to get out of the CAD library business and refer their customers to existing 3rd party CAD Land Pattern libraries.

#### **PCB CAM Vendors:**

The CAM vendors are the last quality control front where the CAD Land Pattern library parts are checked for manufacturability. This is where many the CAD Land Pattern library parts errors are discovered and the manufacturing process has to stop and send the error report back to the PCB designer to correct the errors before proceeding the manufacturing process. Unfortunately, most CAM software DRC checks only detect fabrication errors and not assembly errors.

#### Standards Organizations:

The Standards Groups are responsible for producing guidelines and specifications for proper CAD Land Pattern construction. Unfortunately they cannot keep pace with the rapidly expanding growth of the electronic component industry. So the only alternative for the standards groups is to create the two items mentioned above to aid with the process of standardization of the creation of a one world standard CAD Land Pattern library.

#### Component Manufacturers:

The Component manufacturers have the option of using predefined standard component package data, but often ignore the standards for several reasons. The primary reason is to create a unique package that requires a unique Land Pattern is so the customer who purchases the components is forced to use that specific vendors device and cannot substitute the device with alternative price competitive devices. Also, the reality of the burden of providing CAD Land Patterns should fall on the component manufacturers. The component manufacturer should provide the component dimensional data, the land pattern library part (in a neutral CAD data format) and the land pattern dimensional data to their customers.

The American component manufacturers belong to the organization called NEMI. The Asian component manufacturers belong to the organization called JEITA.

#### IPC-2581 Neutral CAD Database Format

A neutral CAD database format has always been a known fact to support electronic product design and development and failure to create and accept a neutral CAD database format has stifled the automation process. The IPC-2581 neutral CAD database format will fulfill a 30 year search for a universal acceptable format. This one single aspect can greatly accelerate the process of all electronic product development because it is the common language between all machines: The CAD system, the fabrication equipment and the assembly equipment. The IPC-2581 also provides the component manufacturers a mechanism to build their own CAD land patterns using a single intelligent format that can be imported into every CAD tool. This will eliminate millions of man hours spent on CAD Land Pattern Library creation. Used in conjunction with the IPC-7351 land pattern guideline specification, all CAD Land Pattern parts can be created using the same identical universal standard.

The IPC-7351 and the IPC-2581 are the key components that will ultimately standardize The CAD Library of the Future and once and for all put an end to the chaos that has stifled electronic product development automation.

Later in 2004, the industry will discuss validation techniques through building test samples and how tools can become certified in being able to read and write the new format.

#### Transitioning to the Metic System

#### Metrication of the PCB Design Industry

The United States is now the only industrialized country in the world that does not use the metric system as its predominant system of measurement.

Congress, recognizing the necessity of the United States' conformance with international standards for trade, included new encouragement for U.S. industrial metrication in the Omnibus Trade and Competitiveness Act of 1988. This legislation amended the Metric Conversion Act of 1975 and designates the metric system as the preferred system of weights and measures for United

States trade and commerce. The legislation states that the Federal Government has a responsibility to assist industry, especially small business, as it voluntarily converts to the metric system of measurement.

The current effort toward national metrication is based on the conclusion that industrial and commercial productivity, mathematics and science education, and the competitiveness of American products and services in world markets, will be enhanced by completing the change to the metric system of units. Failure to complete the change will increasingly handicap the Nation's industry and economy.

Companies sometimes ask whether they must convert to the metric system of measurement. The simple answer is no -- the law does not require conversion and the government cannot force businesses to convert. Competitors (especially overseas competitors) might even prefer that U.S. companies not convert. Finally, some workers may be relieved to hear they do not need to learn a new system, and companies may wish to postpone transition expenses (although the competitive reality is that postponement will be very temporary and subsequent costs may be higher).

A better answer is yes--yes to a conscious and strategic decision convert. Companies that delay conversion will lose some of the future economic benefits that will ultimately surpass any short-term costs. Companies should convert if they make or sell any product or service that they or anyone else might want to sell in foreign markets, if they want to be assured of being able to sell to the government in the future, and if they want to begin to enjoy a long-term return on their investment in the transition. In short, companies should actively plan and manage their transition, and not wait for circumstances that will force it. By then, it may be too late for some firms to survive in the increasingly competitive business climate.

Clearly, U.S. companies that do not produce products or services to metric specifications will risk being increasingly noncompetitive in world markets. Japan has identified the U.S. lack of metric usage as a strategic impediment to access of U.S. products to the Japanese home market. In addition, consolidation of the European market product standards will make sales of non-metric products increasingly difficult and uncertain. Most U.S. companies understand that using metric units is essential to future economic success. Their hesitation may be due to uncertainty as to when and how to convert.

Through their actions, federal agencies are demonstrating an increasing determination to use the metric system of units in business-related activities. The results are not yet very visible to the public, which is not a direct target of current federal transition activities. Industry is the target, and is becoming increasingly aware of and generally welcomes the government's progress.

Industry acceptance of the wisdom of proceeding with the metric transition is due partly to the realization that producing to metric specifications and surviving in tomorrow's economic environment are synonymous. Industry also understands that government agencies are committed to working cooperatively with industry.

All the World Standard Groups involved in the electronics industry (IPC, IEC, NIST, JEDEC, EIA & JEITA) have made the transition to the metric measurement system. They formed an alliance to stop using English units and all the data they publish is in metric units. The "CAD Library of the Future" will be in metric units.

#### Conclusion

IPC in conjunction with IEC and the world electronics industry standards groups are in the process of establishing the IPC-7351 standard for CAD Land Pattern specifications.

The IPC-7351 specification introduces the following standards for CAD Libraries:

- 1. A strict Land Pattern Naming Convention which will help the standardization of electronic schematic symbols for engineering.

- 2. Zero Component Rotation so that all CAD Land Patterns are built with the same rotation for the purpose of assembly machine automation.

- 3. 3-Tier specification that supports various levels of product complexity. The 3-Tier CAD library system supports the following:

- a. Least Environment Land Pattern for miniature devices where the land pattern has the least amount of solder pattern to achieve the highest component packing density.

- b. Nominal Environment Land Pattern for normal everyday consumer devices. The solder pattern is average size.

- c. Most Environment Land Pattern for high shock, high vibration or life support systems. The solder pattern is robust and can be easily reworked.

- 4. Placement Courtyard has been redefined to accommodate the 3-Tier specification.

- 5. Silkscreen and polarity marking sizes, copper to ink clearances and locations have been clearly defined.

- 6. Land Pattern origins to aid pick and place machine automation has been defined.

- 7. Mathematical algorithms to determine pad sizes and spacing have been defined for the 3Tier environment. These algorithms account for fabrication and assembly tolerances and component tolerances to calculate a precise land pattern.

- 8. 3D Modeling for mechanical verification using maximum component outlines and maximum component height has been defined.

The IPC-7351 defines all the properties necessary for standardization and acceptability of a "One World CAD Library". The main objective in defining a one world CAD library is to achieve the highest level of "Electronic Product Development Automation".

On the other hand, not incorporating a standard CAD library specification will only prevent the highest level of "Electronic Product Development Automation" from happening.

Many large firms have spent millions of dollars creating and implementing their own unique standards for their own "Electronic Product Development Automation". These standards are proprietary to each firm and are not openly shared with the rest of the industry. This has resulted in massive duplication of effort costing our industry millions of man hours in waste and creating industry chaos and global non-standardization.

The IPC-7351 puts an end to "Proprietary Intellectual Property" and introduces a world standard so every electronics firm can benefit from Electronic Product Development Automation.

#### Acknowledgement

It is important to note the key contributors to the development of the IPC-7351 and IPC-2581 standards. The group of representatives is called the IPC 2-17 subcommittee and it consists of the 16 following corporations:

| - Celestica            | - Toppan           |

|------------------------|--------------------|

| - Sanmina-SCI          | - Ohio Design      |

| - Teradyne             | - Router Solutions |

| - Lockheed Martin      | - PCB Libraries    |

| - Valor                | - Mentor Graphics  |

| - Lucent Technologies  | - Cadence          |

| - Agilent Technologies | - IPC              |

| - Solectron            | - NIST             |

|                        |                    |

# The CAD Library of the Future

What PCB Designers need to know about building CAD Library Parts that will help automate the future of all Electronic Product Development

COUNC

## PRESENTED BY: Tom Hausherr

### Director of Technology Tom@PCBLibraries.com

ESIGNERS

DOUNC

### INTRODUCTION

Every electronic component requires a solder land pattern for PCB layout. The solder pattern can be placed into two categories.....

1. Meet all the industry standard requirements for the sole purpose of electronic product creation automation.

2. Fail to meet the industry standard requirements and create electronic product creation chaos.

The CAD Library of the Future will be a "One World Standard Library" that will be accepted by the electronics industry to eliminate duplication of effort and automate all of the engineering, design layout, and the manufacturing and assembly processes.

The following pages explain the criteria needed to create "The CAD Library of the Future". But first, let's meet the key players whose goal is to standardize the electronics product development industry.

ESIGNERS COUNC

### LAND PATTERN NAMING CONVENTION

| Family | Pitch | Lead Span | Pin Qty |

|--------|-------|-----------|---------|

| SO     | 1.27  | 0.710     | 14      |

| SOP    | 0.65  | 0.710     | 14      |

| SSOP   | 0.50  | 0.710     | 14      |

| TSOP   | 0.65  | 0.710     | 14      |

| TSSOP  | 0.50  | 0.710     | 14      |

### Example: TSSOP50P710-14N

### **JEDEC Component Lead Forms**

JEDEC Standard No. 30-B Page 18

LAND STRUCTURE

Component Lead Space Tolerance This Solder Joint Tolerance is for the inside dimension between the component terminal. It is normally represented by the "S" symbol. See the pictures below as a reference

### SOLDER JOINT TOLERANCE

Land Pattern Pad Length Tolerance The "G" dimension is used to calculate the minimum and maximum inside spacing of the solder pad. The "Z" dimension is used to calculate the minimum and maximum outside spacing of the solder pad. See pictures

SIGNERS

COUNC

### SOLDER JOINT ANALYSIS

**Solder Joint Toe, Heel and Side Goal** The chart below provides an example of the Gull Wing component lead Solder Joint Goal

Round or flattened (coined) leads (unit: mm)

| Land pattern<br>characteristics | Maximum<br>Level 1 | Median<br>Level 2 | Minimum<br>Level 3<br>0,2 |  |

|---------------------------------|--------------------|-------------------|---------------------------|--|

| Toe-land protrusion             | 1,0                | 0,65              |                           |  |

| eel-land protrusion 0,5         |                    | 0,35              | 0,2                       |  |

| Side-land protrusion            | 0,1                | 0,1               | 0,1                       |  |

| Courtyard excess 0,5            |                    | 0,25              | 0,05                      |  |

| Round-up factor                 | Nearest 0.5        | Nearest 0.5       | nearest 0.05              |  |

### SOLDER JOINT ANALYSIS

The illustration below provides a graphical representation of the Gull Wing component lead to calculate the Toe, Heel and Side minimum and maximum values

Zmax = Lmin + 2JTmin + TT Where: JTmin = Minimum toe fillet TT = Combined tolerances at toe fillet

Heel Fillet

Gmin = Smax - 2JHmin - TH Where: JHmin = Minimum heel fillet TH = Combined tolerances at heel fillet

Xmax = Wmin + 2JSmin + TS Where: JSmin = Minimum side fillet TS = Combined tolerances at side fillet

### SOLDER JOINT ANALYSIS

### **Solder Joint / Land Protrusion**

- J is the desired dimension of solder fillet or land protrusion;

- → J<sub>t</sub> is the solder fillet or land protrusion at toe;

- ↓ *J<sub>h</sub>* is the solder fillet or

land protrusion at heel;

- J<sub>s</sub> is the solder fillet or land protrusion at side;

### **MANUFACTURING TOLERANCE**

- Fabrication Tolerances

- Assembly Tolerances

- Component Terminal Tolerances

### Land Pattern Equations

- $Z_{max} = L_{min} + 2J_T + \sqrt{C_L^2 + F^2 + P^2}$

- $G_{min} = S_{max} 2J_H \sqrt{C_L^2 + F^2 + P^2}$

- $X_{max} = W_{min} + 2J_S + \sqrt{C_L^2 + F^2 + P^2}$

- where

IPC

- Z is the overall length of land pattern;

- > G is the distance between lands of the pattern;

- > X is the width of land pattern;

# **ZERO COMONENT ROTATION**

The Component Zero Rotation relates to the **Pick & Place machine tape and reel and** component tubes. The rotation of the actual component in the tube or tape & reel is referred to as the Zero Rotation for the CAD Library part and how it should be built in the CAD library. All CAD Library parts should be built in the CAD system in the same rotation that the component is packaged in the tape and reel or assembly feeder tube.

The JEDEC JEP95 specification is the industry guideline for component packaging information and Component Zero Rotation.

COUNC

ESIGNERS

# ZERO COMONENT ROTATION

- 1) Chip, Molded, MELF Capacitors, Resistors and Inductors (RES, CAP and IND) Pin 1 (Positive or Cathode) on Left

- 2) SOT Devices (SOT89, SOT143, etc.) Bottom Left

- 3) TO 252/268 Devices Bottom Left

- 4) Small Outline Gullwing ICs (SOIC, SOP, TSOP, etc.) Bottom Left

- 5) TSSOP packages with leads protruding from short side of body (Whenever the component body width is longer than the component body length) Left Top

- 6) Small Outline J Lead ICs (SOJ) Bottom Left

- 7) Quad Flat Pack ICs (PQFP, SQFP) Bottom Left

- 8) Ceramic Quad Flat Packs (CQFP) Left Top

- 9) Ceramic Flat Packs (CFP) Bottom Left

- 10) Plastic Leaded Chip Carriers (PLCC) Left Center

- 11) Leadless Chip Carriers (LCC) Top Center

- 12) Quad Flat No-Lead ICs for QFNS & QFNRV (Vertical) Left Bottom

- 13) QFNRH (Horizontal) Outlines Top Left

- 14) Ball Grid Arrays (BGA) Bottom Left

IPC

DESIGNERS (BOUNCI

2

# LAND PATTERN ORIGIN

The land pattern origin is the component "Center of Gravity" so in most cases it's the Center of the library part. An example of where it's not the center is the DPAK or TO-252 component.

## PLACEMENT COURTYARD

The primary use of the placement courtyard was to provide the PCB designer a guideline for placing land patterns next to each other with enough room to compensate for component tolerances.

ESIGNERS NOUNCI

### LAND PATTERN COURTYARD DETERMINATION Land Pattern Courtyard **Determination** Component / pattern (maximum boundary) Courtyard $\cap$ excess Courtyard <u>(minimum area)</u> Manufacturing allowance Courtyard manufacturing zone IPC DESIGNERS COUNCIL

## SILKSCREEN OUTLINE

Silkscreen outlines are used for cosmetic purposes only and are really not required by manufacturing.

The silkscreen can be drawn by the PCB designer very complex to illustrate their creative talent or very simple. In the end, it really doesn't matter because you can only see it when the physical PC board passes between the fabrication facilities to the assembly shop. Once the parts are assembled, all the silkscreen outlines are covered up and cannot be seen.

➢ When PCB designers start to use all the principles discussed in this outline, the manufacturing assembly process can be fully automated and silkscreen component outlines will not be required.

ESIGNERS

COUNC

COUNC

#### SILKSCREEN POLARITY MARKINGS

The term Polarity Marking came from its use to identify the Positive Pin on a "Polarized" capacitor. But polarity marking is also used on Diodes to indicate the Cathode Pin.

Polarity Markings are also used when there is a potential for inverting the part placement in the assembly process that would result in a malfunction of the component.

## **ASSEMBLY OUTLINE**

The assembly drawing outline should represent the maximum outline of the component body. Unlike the silkscreen outline which has to be created to avoid solder pads (a fake component outline); the assembly outline only gets placed on an assembly drawing that goes to the assembly shop.

Here is some sample assembly drawing component outlines in relationship to the solder pad

## **ASSEMBLY POLARITY**

The assembly Polarity Marking is sometimes totally different than the silkscreen Polarity Marking because the silkscreen must avoid touching the component solder pad

C DUN

## **SMT PADSTACKS**

The surface mount component padstack consists of a solder pad, solder mask and solder paste. We've already discussed the creation of the pad size. The solder mask and paste mask size is typically the same as the pad size.

Solder Mask - We allow the PC Board manufacturer expand the solder mask size according the rule technology that the PCB designer used to design the PCB layout.

Solder Paste – We allow the stencil maker to oversize the solder paste to match the specifications of the assembly shop that the paste mask stencil is being made for.

## THROUGH HOLE PADSTACKS

- This is what a typical Through Hole Padstack is built like:

- Top Solder Mask

- Top Pad

- Inner Layer Pad

- Plane Anti-pad

- Plane Thermal Relief

- Bottom Pad

- Bottom Solder Mask

- Drilled Hole

# **3D COMPONENT OUTLINE**

Every CAD tool has a different approach to handling 3D Models of component data. Some are much more elaborate than others.

The CAD Library of the Future will have 3D Model attributes built into every land pattern to use as a mechanical drafting aid for the reduction of errors in product packaging.

## IPC-7351 3-Tier LIBRARY SYSTEM

Here are the three different tiers and how and when you should use them:

- Most for boards that are subjected to high shock/vibration or are involved in life support such as automotive, aerospace, medical applications and military products IPC Performance Level A "High Reliability Electronic Products"

- Nominal for boards that are in devices that require only average dependability such as consumer applications, computers, appliances and home entertainment systems IPC Performance Level B "Dedicated Service Electronic Products"

- Least for boards that are thrown away if they break or need service such as cell phones, Palm Pilots, toys, PCMCIA boards or very dense boards. IPC Performance Level C "General Electronic Products"

ESIGNERS COUNC

IPC

DESIGNERS (OUNCIL

#### IPC-7351 3-Tier LIBRARY SYSTEM

<u>Land Pattern Variations</u> <u>for</u> <u>Rectangular Two Terminal Devices</u>

Level A Very Robust Solder Joint Level B General Purpose Solder Joint Level C Minimal Solder Joint for High Density Applications

### Free IPC-7351 Libraries

PCB Libraries builds all "IPC-7351 Standard SMT Library Parts", free of charge, for PADS-PowerPCB<sup>™</sup> V4 & V5. One of PCB Libraries goals is to build every standard part in the world and offer it for free download on www.PCBLibraries.com to initially to every PADS<sup>™</sup> user and eventually to every CAD Tool via IPC-2581 format.

Here is a list of Standard IPC-7351 SMT parts:

- BGA • QFN

- QFP • SOJ

- SQFP • PLCC

- TQFP

- SOIC

- SOP

- TSOP • CFP

- •TSSOP • CQFP

• LCC

- Chip Resistor, Capacitor and Inductor

- Aluminum Electrolytic Capacitors

- Tantalum Capacitor

- SOT Molded Inductor

- MELF Wire Wound Inductor

- Molded Resistor, Diode

- TO Packages

- All JEDEC Standard Components

## IPC-2581 NEUTRAL CAD FORMAT

A neutral CAD database format has always been a known fact to support electronic product design and development and failure to create and accept a neutral CAD database format has stifled the automation process.

The IPC-2581 neutral CAD database format will fulfill a 30 year search for a universal acceptable format. This one single aspect can greatly accelerate the process of all electronic product development because it is the common language between all machines: The CAD system, the fabrication equipment and the assembly equipment.

The IPC-2581 provides component manufacturers a solution to build their own CAD land patterns using a single intelligent database format that can be imported into every CAD tool.

COUNC

DOUNC

#### TRANSITIONING TO THE METIC SYSTEM

The United States is now the only industrialized country in the world that does not use the metric system as its predominant system of measurement.

All the World Standard Groups involved in the electronics industry (IPC, IEC, NIST, JEDEC, EIA & JEITA) have made the transition to the metric measurement system. They formed an alliance to stop using English units and all the data they publish is in metric units.

SIGNERS

COUNC

#### TRANSITIONING TO THE METIC SYSTEM

The current effort toward national metrication is based on the conclusion that industrial and commercial productivity, mathematics and science education, and the competitiveness of American products and services in world markets, will be enhanced by completing the change to the metric system of units. Failure to complete the change will increasingly handicap the Nation's industry and economy.

#### TRANSITIONING TO THE METIC SYSTEM

The "CAD Library of the Future" will be built in metric units

IPC

DESIGNERS COUNCIL