# Development of high density and high frequency substrate using $B^2it^{TM}$ technology for next generation

IPC annual Meeting November 5, 2002

Satoru Kuramochi Tomoko Maruyama Miyuki Akazawa Kouichi Nakayama Masataka yamaguchi Atsushi Takano Kazuo Umeda \* Osamu Shimada\* Yoshitaka Fukuoka \*\*

Dai Nippon Printing Co., Ltd.

\*D.T.circuit technology Co., Ltd.

\*\* Weisti(worldwide Electronic Integrated Substrate Technology Inc)

# **Contents**

- 1, Background

- 2, Concept of Development

- 3, Fabrication Process

- 4, Electrical Characteristic

- 5, Summary and Future plan

IPC annual Meeting

November 5, 2002

# 1, Background

### Technology nodes for High density packaging substrate

|                                      | 2002        | 2004        | 2005 | 2007 | 2010 | 2016       |

|--------------------------------------|-------------|-------------|------|------|------|------------|

| Technology<br>Nodes (nm)<br>MPU/ASIC | 180         | 90          | 80   | 65   | 50   | 26         |

| Needs                                |             |             |      |      |      |            |

| for BGA                              |             |             |      |      |      |            |

| Ball-Pitch                           | 0.4         | 0.4         | 0.4  | 0.3  | 0.3  | 0.25       |

| (mm)                                 |             |             |      |      |      |            |

| FcpadPitch                           | 0.16        | 0.15        | 0.13 | 0.12 | 0.09 | 0.07       |

| (mm)                                 |             |             |      |      |      |            |

| Line ( um )                          | <b>10.7</b> | <b>10.7</b> | 9.2  | 9.2  | 6.4  | <b>5.0</b> |

| Space ( um )                         | 10.7        | 10.7        | 9.3  | 9.3  | 6.4  | 5.0        |

| Performance                          |             |             |      |      |      |            |

|                                      |             |             |      |      |      |            |

| On-chip(GHz)                         | 2.32        | 3.09        | 5.17 | 6.74 | 12   | <b>29</b>  |

| Performance                          |             |             |      |      |      |            |

| Chip-to-Board                        |             |             |      |      |      |            |

| For peripheral                       |             |             |      |      |      |            |

| Buses(GHz)                           | 1.87        | 2.26        | 2.49 | 3.01 | 4.0  | 7.1        |

Source

ITRS2001Edition

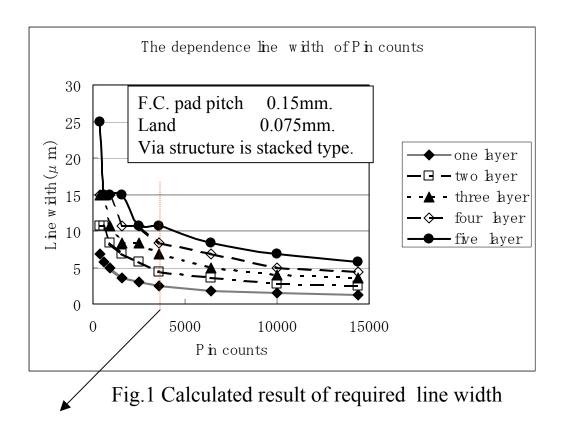

### Calculated result of required line width

3600 pin count FC-package needs 8.3um line width by 4layer, or 10.7um line width by 5layer.

### **Motivation**

Why do we conduct this study?

Package pin count overflow

interconnection delay

Development of Substrate

Line width under 10um for fine pitch

High performance at high frequency over 9GHz

Based on new type of substrate

B<sup>2</sup>it<sup>TM</sup> technology

# 2, Concept of Development

# We have developed B<sup>2</sup>it<sup>TM</sup> Printed Wiring Boards

**B**<sup>2</sup>it<sup>TM</sup> Bump Shape ( After Printing )

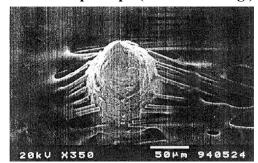

B<sup>2</sup>it<sup>TM</sup> Bump Shape ( After Piercing )

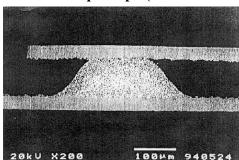

**B**<sup>2</sup>it<sup>TM</sup> Bump Shape ( After Lamination )

- **①Great variety of multilayer structure and process.**

- **2**Stacked (Straight) via holes of great advantage to area I/O terminal devices.

**3High cost-performance printed wiring board.**

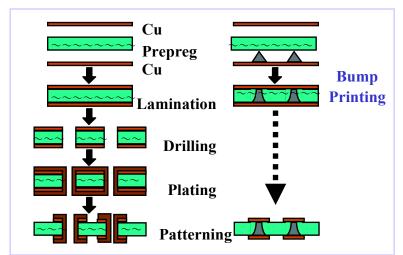

Process Comparison between B2itTM & standard PWB.

# We propose new structure for next generation

Table 2 B<sup>2</sup>it<sup>TM</sup>Design Rules

|             | Standard       | Fine   | Fine   | Fine    |  |

|-------------|----------------|--------|--------|---------|--|

|             |                | Phase1 | Phase2 | Phase3  |  |

| Build up la | Build up layer |        |        |         |  |

| L/S         | -              | -      | _      | Under   |  |

|             |                |        |        | 10/10   |  |

| Via         | -              | -      | _      | Under   |  |

| /Land       |                |        |        | 20/30   |  |

|             |                |        |        | stack   |  |

| Core        |                |        |        |         |  |

| L/S         | 100            | 75     | 50     | 30      |  |

|             | /100           | /75    | /50    | /30     |  |

| Bump        | 300            | 150    | 100    | 100     |  |

| Diameter    |                |        |        |         |  |

| Pad         | 500            | 300    | 200    | 200     |  |

| Diameter    |                |        |        |         |  |

| Bump        | 600            | 400    | 300    | 300     |  |

| Pitch       |                |        |        |         |  |

|             | ı              |        | •      | (22400) |  |

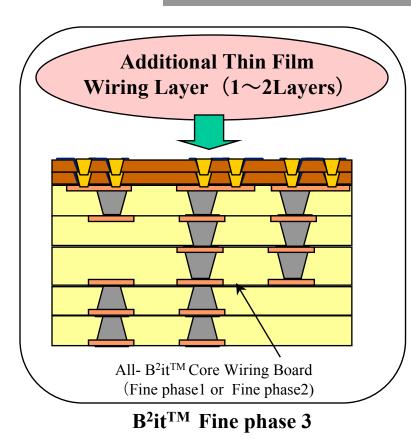

Combination

Additional Thin Film

Wiring Layer

(1~2Layers)

(Fine phase1 or Fine phase2)

(um)

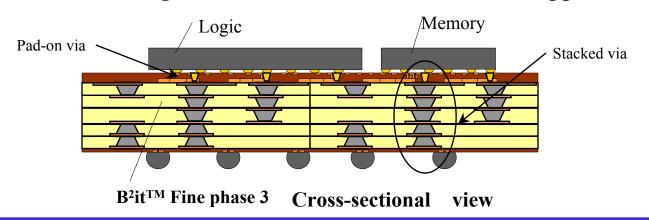

# **B**<sup>2</sup>it<sup>TM</sup> Fine phase 3 Concept

Equal Wiring Network

**Conventional Plugged**

**Double Side Wiring Board**

900pin FC0.15 L/S=8.3/8.3

Fan out 2Layer

900pin FC0.15 L/S=25/25

**Repetitions of Process**

Low Yield

Plugged Core

Fan out 7Layer

### Features of B<sup>2</sup>it<sup>TM</sup> Fine phase 3

- 1, High-Performance  $\Rightarrow$  High speed transmission over 9GHz

- 2, Fine wiring, high density, precise

⇒L/S=Under10um/10um, V/L=Under20/30um stacked Straight Via ( Stacking Via ) holes are available.

#### 3, Cost-performance

$\Rightarrow$  B<sup>2</sup>it<sup>TM</sup> Fine phase 3 substrate can be applied to all kinds of devices with grid I/O terminals . SIP is best application.

# 3, Fabrication Process

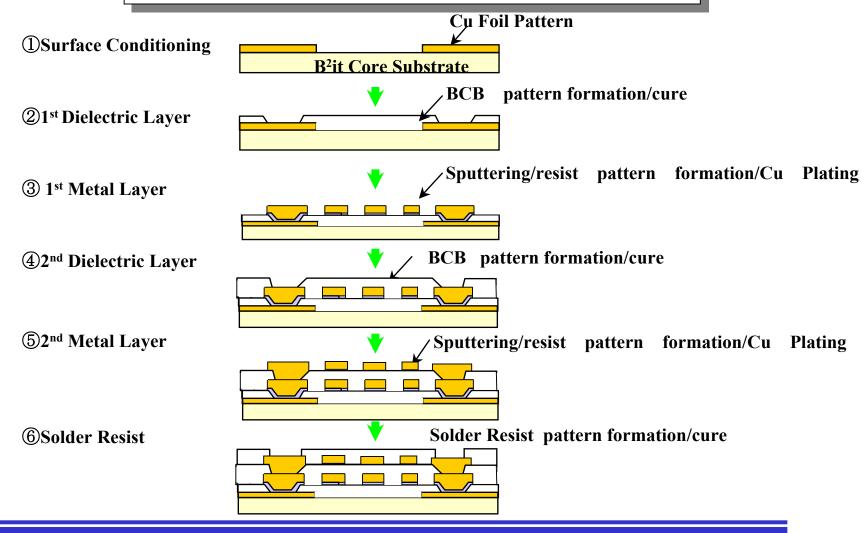

# **Process** of B<sup>2</sup>it<sup>TM</sup> Fine phase 3

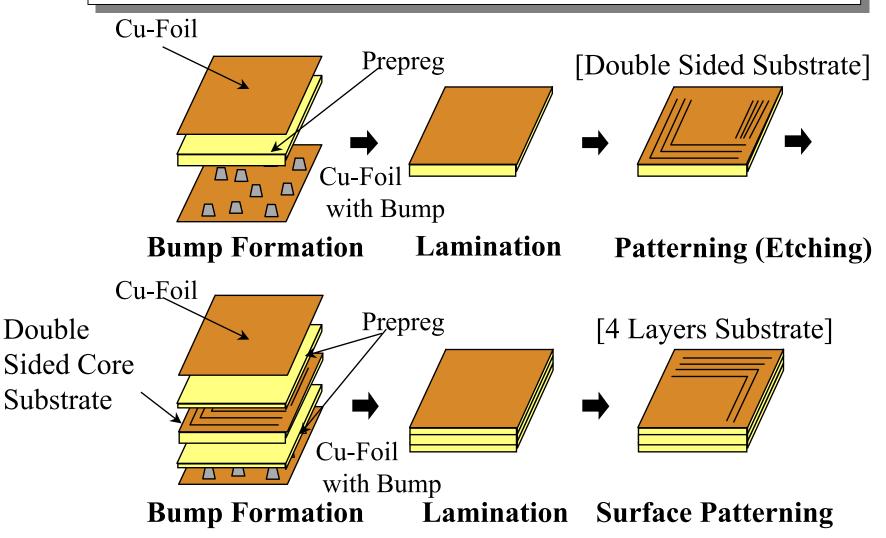

# **B**<sup>2</sup>it<sup>TM</sup> Core substrate Manufacturing Process

# **Reliability Test Results**

| No | Item                                   | Condition                            | Criteria                                                       | Result |

|----|----------------------------------------|--------------------------------------|----------------------------------------------------------------|--------|

| 1  | Peel Strength                          | Peeling Speed 500mm/min              | 1.4kN/m(1.43kgf/cm)                                            | OK     |

| 2  | Soldering Endurance                    | 260°C, 20sec & 288°C, 10sec          | Resistivity Changing Ratio less than 10%                       | ОК     |

| 3  | Insulating Voltage                     | DC500V, 60sec                        | No damage                                                      | ОК     |

| 4  | Temperature<br>Humidity Cycle          | 25°C⇔65°C∕90~98% 10Cycle(<br>240H)   | Insulating Resistance more than $5 \times 10^7 \Omega$         | ОК     |

| 5  | High Temperature<br>High Humidity Bias | 85℃/85%、DC12V&60V 500H               | Insulating Resistance more than $5 \times 10^7 \Omega$         | ОК     |

| 6  | Temperature Cycling                    | -65°C (30min) ⇔125°C (30min) 1000cy  | cResistivity Changing Ratio less than 10%                      | ОК     |

| 7  | Hot Oil (Thermal Shock)                | 260°C (10sec) ⇔20°C (20sec) 100Cycle | Resistivity Changing Ratio less than 10%                       | OK     |

| 8  | Pads Pull Strength                     | 90° Pull head Speed :10mm/min        | 10N/mm <sup>2</sup>                                            | ОК     |

| 9  | High Temperature<br>Operation          | 100℃、0.3A、1000H                      | Resistivity Changing Ratio less than 10%                       | ОК     |

| 10 | HAST                                   | 130℃/85%、DC10V、100H                  | Leak Current less than 10 <sup>-10</sup> A                     | ОК     |

| 11 | Bending                                | ±10% Bending 100 Cycle               | Resistivity Changing Ratio less than 10%                       | ОК     |

| 12 | Corrosion Gas                          | H2S: 0.1ppm, SO2: 0.5ppm 12V, 500    | <b>H</b> nsulating Resistance more than $5 \times 10^7 \Omega$ | ОК     |

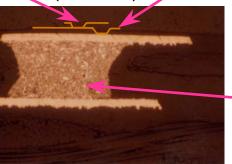

# Fine wiring technology

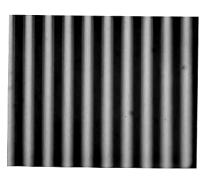

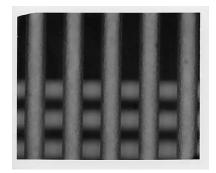

#### Sputter-semi-additive method

(1) Sputtering thin metal

(2) Resist formation

(3) Filled plating

(4) Remove resist and thin metal

(a) L/S=6um/4um (3  $\sigma$  = 0.46 u m)

(c) L/S=8um/7um  $(3 \sigma = 0.53um)$

(b) L/S=6um/4um profile o f 2Layer

(d) L/S=11 u m/9 u m (3  $\sigma$  =0.41um)

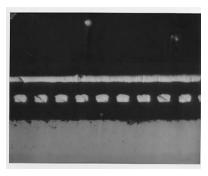

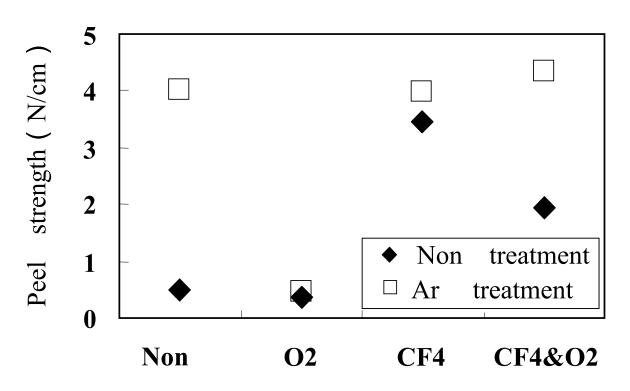

# Treatment effect before sputtering

Pre-treatment surface of insulator by dry etching gas

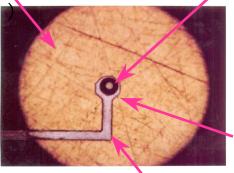

# Photo Via on B<sup>2</sup>it<sup>TM</sup> Core

Core B<sup>2</sup>it<sup>TM</sup> Land (dia.400um Via Diameter 30um

Land Diameter

60um

Line Width 30um

**Interconnection Over View**

Photo Via (dia30um) L/S: 30/30um

$B^2it^{TM}$  Bump (dia.200um)

**Interconnection Cross Sectional View**

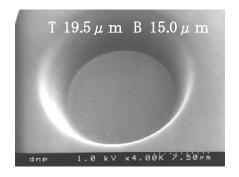

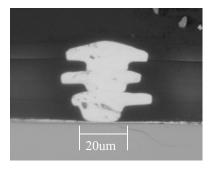

### Filled via technology

Via/Land=20um/30um stacked structure

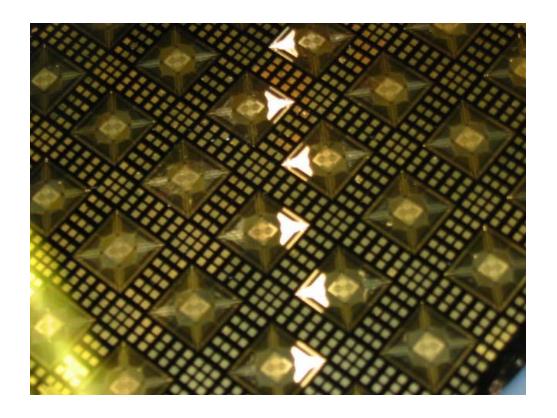

# Appearance of a prototype

# 4, Electrical Characteristic

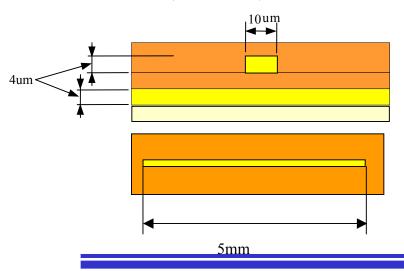

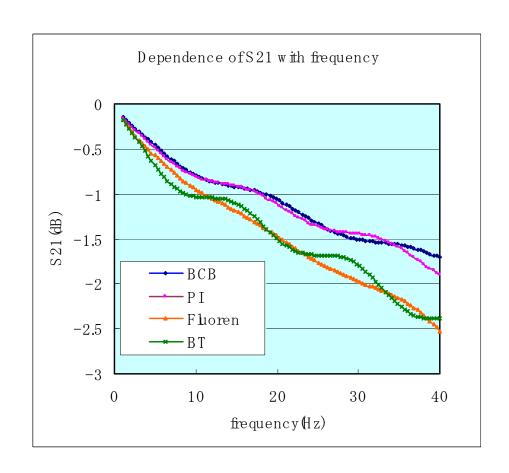

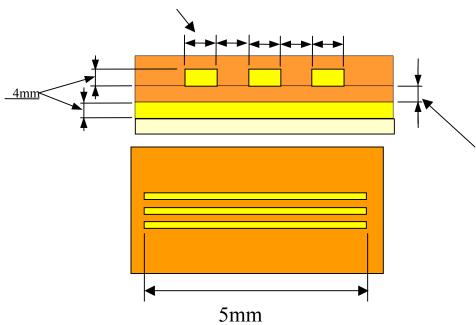

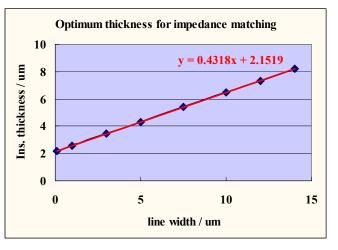

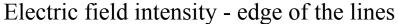

### Simulation result of transmisson characteristic

Simulator; HFSS(Ansoft) High frequency stress simulator

Model: Microstlip line with cover layer

#### Simulation structure

| Insulator | 3   | $tan \delta$ |

|-----------|-----|--------------|

| BCB       | 2.7 | 0.0009       |

| PI        | 3.2 | 0.0018       |

| Fluorene  | 3.2 | 0.029        |

| BT        | 4.2 | 0.012        |

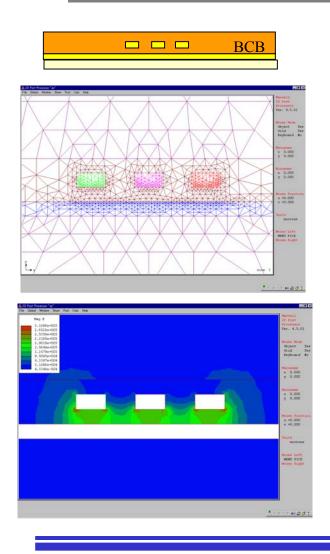

# Simulation structure for evaluation of crosstalk

#### Simulator:

HFSS; High Frequency strucre simulator (Ansoft)

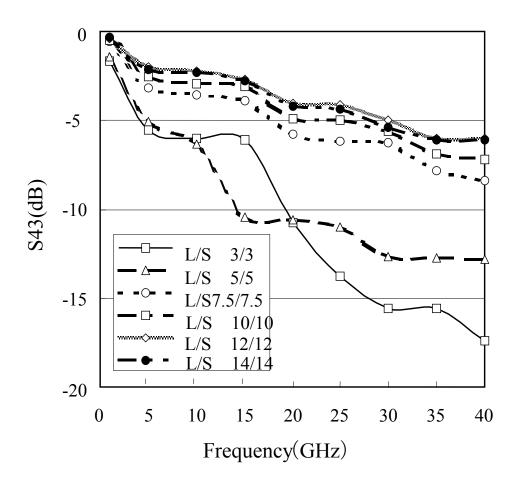

L/S=3/3, 5/5, 7.5/7.5, 10/10, 12/12, 14/14um

The dependence of insert loss on crosstalk of contiguity wiring

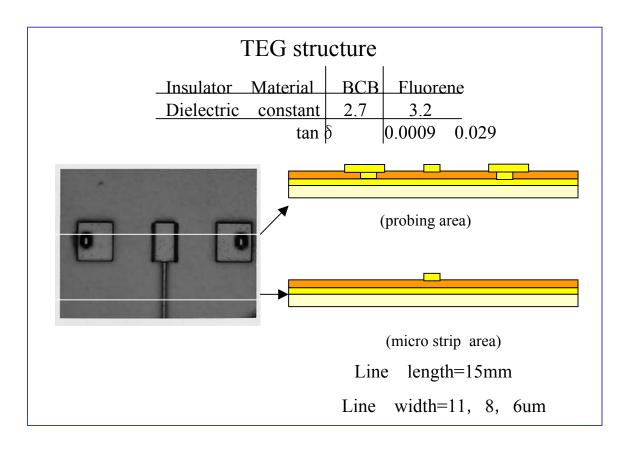

#### TEG structure for measurement of S-parameter

S-parameter measured using network analyzer, HP8722ES which made from Agilent technology

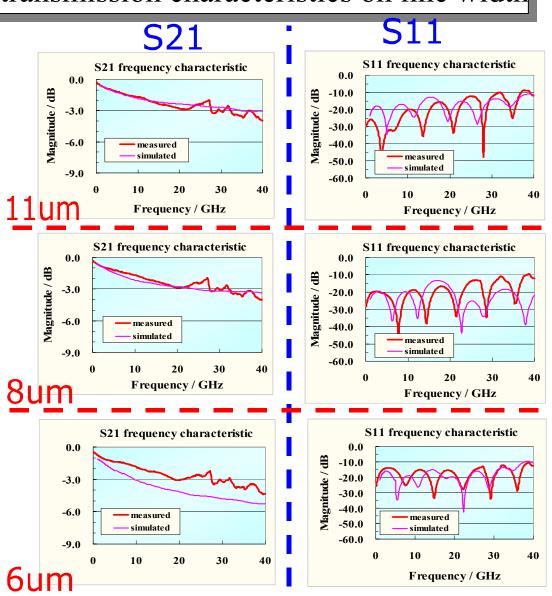

### The dependence of transmission characteristics on line width

Line width 6um, 8um, 11um

line length: 15mm

insulator: **BCB**

A transmission characteristic does not become worth even if line width becomes small.

### Comparison of measurement and simulation

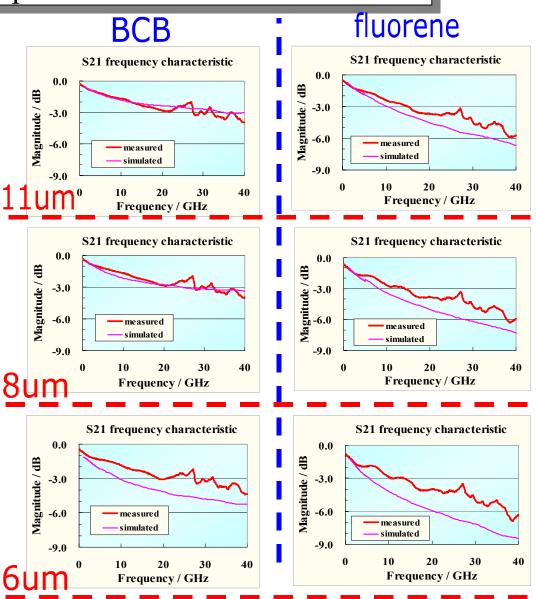

### Comparison of BCB and Fluorene

$S_{21}$  (insertion loss)

Line width 6um, 8um, 11um

line length: 15mm

insulator: BCB / fluorene

# 5, Summary and future plan

- 1, Very fine pitch Cu conductors with BCB on B<sup>2</sup>it<sup>TM</sup> core laminate was developed. The minimum pitch was 10um (L/S=6 /4). Filled plating process was possible for 20um via diameter

- 2, Cu conductors with BCB has excellent high frequency characteristic, it was –3dB in 16GHz.

In case of single line, it does not become worth even if line width becomes small. However, when the pitch became small at 10um or less with contiguity wiring, transmission loss becomes large owing to the crosstalk.

- 3, As a optimal design rule of a the fine wiring layer, pitch is 15 um (L/S=7.5 / 7.5), and 20 um of diameters filled via are the optimal designs, and high density and high-speed substrate,  $B^2 it^{TM}$  fine phase 3 was developed.

- 4, The reliability of interconnection has not conducted yet. We plan to systematic and detailed reliability tests in next stage. We will be sure that it becomes advantageous solution for a high-density and high-speed next-generation package.