North American EMS Industry Up 10.6 Percent in November

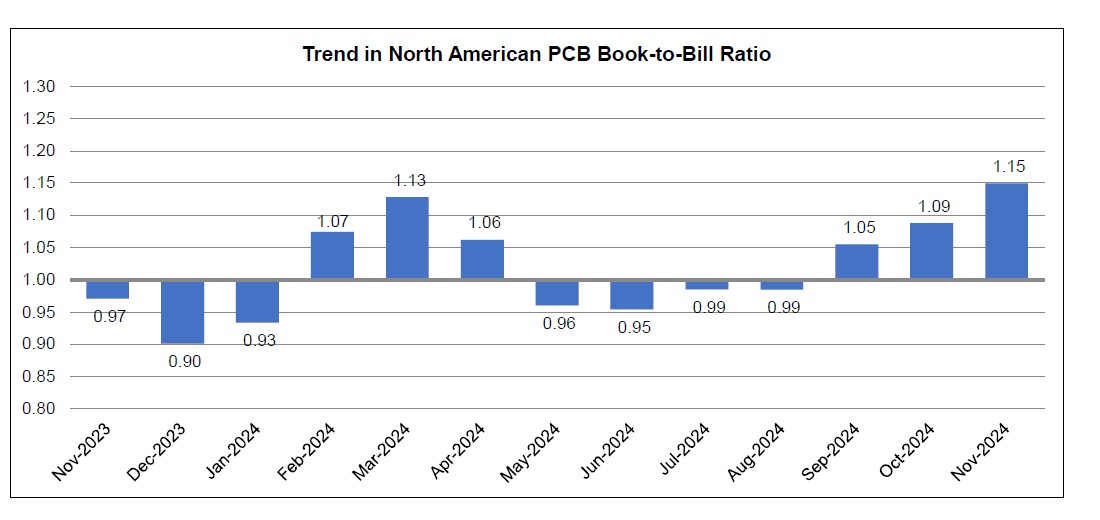

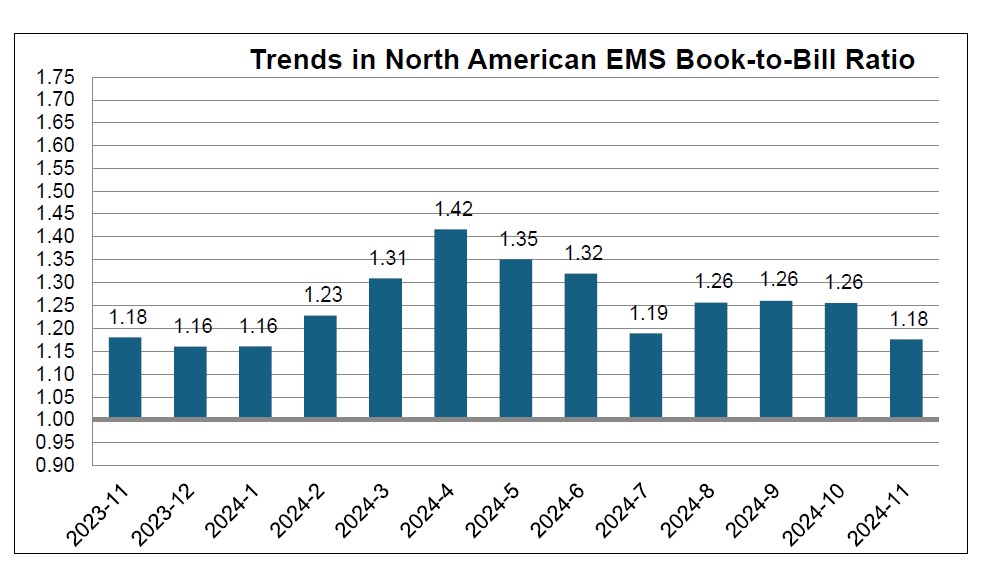

IPC announced today the November 2024 findings from its North American Electronics Manufacturing Services (EMS) Statistical Program. The book-to-bill ratio stands at 1.18.

Total North American EMS shipments in November 2024 were up 10.6 percent compared to the same month last year. Compared to the preceding month, November shipments were up 4.0 percent.

EMS bookings in November increased 8.1 percent year-over-year and decreased 2.7 percent from the previous month.

“EMS order volumes have slowed in recent months, but the year-to-date trend remains steady. This slowdown could signal a short-term pause as businesses wait for better clarity following the inauguration,” said Shawn DuBravac, IPC’s chief economist.

Detailed Data Available

Companies that participate in IPC’s North American EMS Statistical Program have access to detailed findings on EMS sales growth by type of production and company size tier, order growth and backlogs by company size tier, vertical market growth, the EMS book-to-bill ratio, 3-month and 12-month sales outlooks, and other timely data.

Interpreting the Data

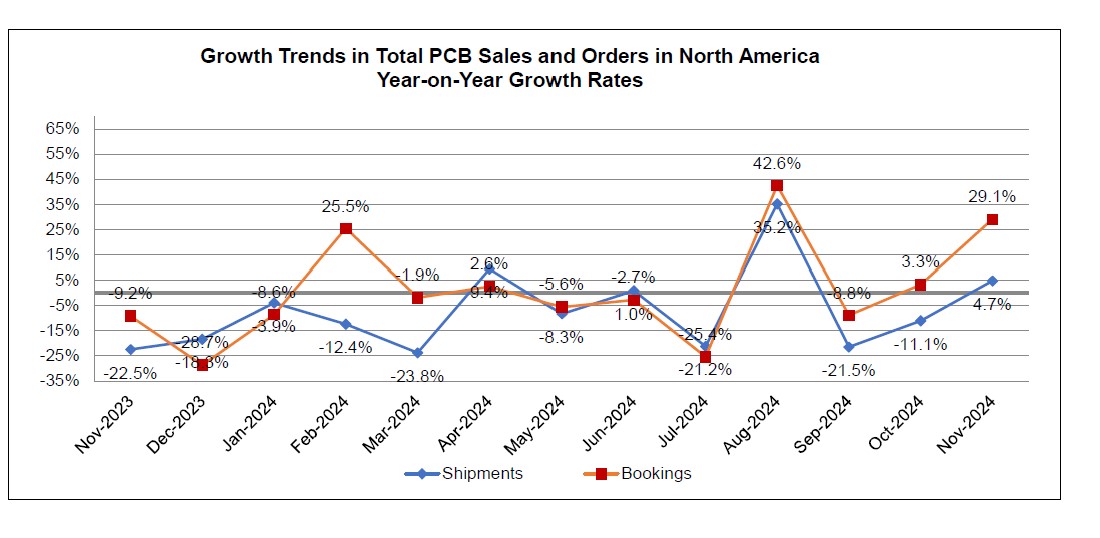

The book-to-bill ratios are calculated by dividing the value of orders booked over the past three months by the value of sales billed during the same period from companies in IPC’s survey sample. A ratio of more than 1.00 suggests that current demand is ahead of supply, which is a positive indicator for sales growth over the next three to twelve months. A ratio of less than 1.00 indicates the reverse.

Year-on-year and year-to-date growth rates provide the most meaningful view of industry growth. Month-to-month comparisons should be made with caution as they reflect seasonal effects and short-term volatility. Because bookings tend to be more volatile than shipments, changes in the book-to-bill ratios from month to month might not be significant unless a trend of more than three consecutive months is apparent. It is also important to consider changes in both bookings and shipments to understand what is driving changes in the book-to-bill ratio.

IPC's monthly EMS industry statistics are based on data provided by a representative sample of assembly equipment manufacturers selling in the USA and Canada. IPC publishes the EMS book-to-bill ratio by the end of each month.